# **Capacitor-less Buck Converter**

UDK 681.586 IFAC 4.3.1

Original scientific paper

Low-power switched-mode power supply converters are used in applications where size and efficiency are critical. The buck converter size can be reduced by elimination of the bulky filter capacitor. The filtering function of this capacitor can be replaced by an output current ripple compensation circuit. The compensating circuit is applied, based on inductor current measurement and linear amplifier. The proposed compensating algorithm is investigated theoretically by simulation, and verified experimentally.

Key words: dc-dc buck converter, low power, inductor current ripple compensation

Silazni DC-DC pretvarač bez izlaznog kondenzatora. DC-DC pretvarači malih snaga se koriste u uredjajima gdje su važni dimenzije i učinkovitost. Dimenzije pretvarača se mogu smanjiti sa izostavljanjem filtarskog kondenzatora. Umjesto sa kondenzatorom se funkcija gladjenja izlaznog napona može izvesti sa kompenzacijom valovitosti struje zavojnice. Za kompenzaciju valovitosti struje je potrebno mjeriti trenutnu vrijednost struje induktora koja se preko obrade u linearnom pojačalu dodaje u protifazi struji zavojnice. Predloženi kompenzacijski postupak je istraživan teoretski te verificirani simulacijski i eksperimentalno.

Ključne riječi: dc-dc silazni pretvarač, mala snaga, kompenzacija valovitosti struje zavojnice

#### 1 INTRODUCTION

Switched-mode power converters (SMPCs) have won the battle over linear power converters (LPCs) because of their high efficiency and small volume. Nevertheless, because traditional approaches for SMPC implementation rely on discrete components, many modern concepts have joined and integrated diverse functionality in to a single integrated power module (IPEM) [1], [2]. There are tremendous efforts being made to replace physical elements with 'smart' algorithms and approaches, for example, it is far more economically justified to improve the electromagnetic compatibility (EMC) of an SMPC using modulation strategy, than with costly and bulky EMI filters [3], [4], [5], [6]. Lower output voltage, higher output current, and smaller output voltage ripple requirements have greatly increased the difficulty of the power supply design. An improved topology of the inductor switching dc-dc converters is shown in [7], [8].

An output filter for reducing converter output voltage ripple is an extremely important part of the buck converter, and often accounts for a significant proportion of its size and costs [9], [10]. The bulkiness of the output LC filter, when output voltage ripple is taken into account, can be overcome by increasing the switching frequency or applying an active power filter. Switching frequency increase is inevitability related to higher switching losses. Regard-

ing to this an interesting approach, was recently published in [11] where the authors describes special dc-dc converter structure capable to reduce the output voltage ripple. Some approaches in the field of audio amplifiers combine the functionalities of LPC and SMPC [12], [13] in order to maintain good device efficiency and low total harmonic distortion (THD).

The following text presents an approach for eliminating the buck converter output capacitor. Such an approach minimizes the converter's volume and is suitable for System-on-Chip (SoC) or System-in-Package (SiP) applications, where the coil remains the only external component necessary for proper system functionality. The inductor current ripple compensation method is proposed, by focusing on the hybrid structured SMPC and LPC. The proposed current ripple compensating algorithm requires closed control loop [13], [14] and [15] in order to keep converter efficiency on the reasonable level. The operation of the proposed circuit is theoretically investigated and verified with simulations and experiments.

# 2 THE BUCK CONVERTER'S CURRENT AND VOLTAGE RIPPLE

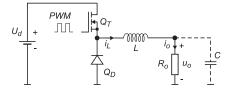

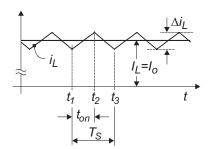

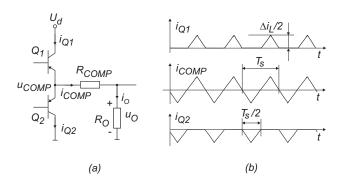

The basic structure of buck converter is shown in Fig. 1 (a). The inductor current ripple  $(\Delta i_L)$  for the buck con-

Fig. 1. (a) Buck converter; (b) Inductor current and output voltage ripples (when C is not applied)

verter in continuous current mode operation without filter capacitor can be estimated by:

$$\Delta i_L = \frac{U_d}{R_o} \left( 1 - e^{\frac{t_{on}}{\tau}} \right)$$

$$= \frac{U_d}{R_o} \left( 1 - e^{\frac{\Delta_p T_s}{\tau}} \right)$$

(1)

where  $U_d$  is the input voltage,  $t_{on}$  is the switch-on transistor time,  $\tau = L/R_o$ ,  $T_s$  is the switching period,  $\Delta_p$  is the duty-cycle  $(t_{on}/T_s)$ , L is the inductance, and  $R_o$  is the load resistance. Fig. 1 (b) shows the inductor current (or the converter output current  $i_L = i_o$ ) and output voltage waveform when the filter capacitor is not applied. The voltage ripple  $(\Delta u_o)$  can be expressed by:

$$\Delta u_o = R_o \Delta i_L \tag{2}$$

In order to create output voltage ripple in (2), the load-independent, the current ripple  $\Delta i_O$  must be appropriately reduced to almost zero.

## 3 INDUCTOR CURRENT RIPPLE COMPENSA-TION PRINCIPLE

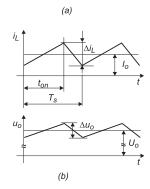

In a steady state the inductor current  $i_L$  (Fig. 2 (a)) can be described as the sum of the DC current component  $(I_L = I_o)$  and the AC current component  $(i_{RIPPLE}(t))$ , as indicated in Fig. 2 (b).

$$i_L(t) = I_o + i_{RIPPLE}(t) \tag{3}$$

Fig. 2. a) Circuit node consideration; (b) Inductor current; (c) node  $N_1$  currents:  $i_L$ ,  $i_o$ , and  $i_{COMP}$

where the DC output current is evaluated by  $I_o = U_o/R_o = \Delta_p U_d/R_o$ , where  $U_o$  is the average value of  $u_o$ . According to the Kirchhoff current law, the converter output current  $i_o$  can be expressed by:

$$i_o(t) = i_L(t) + i_{COMP}(t) \tag{4}$$

And by substituting (3) into (4), yields:

$$i_o(t) = I_o + i_{RIPPLE}(t) + i_{COMP}(t)$$

(5)

In order to eliminate current ripple the instantaneous current  $i_o$  must be equal to its average value  $I_o$ , so from (5) it follows that:

$$i_{COMP}(t) = -i_{RIPPLE}(t) \tag{6}$$

It is evident from (6), that the compensating current  $i_{COMP}(t)$  must have the same magnitude as  $i_{RIPPLE}(t)$  and must be phase-shifted by  $180^{o}$ , as is shown in Fig. 2 (c).

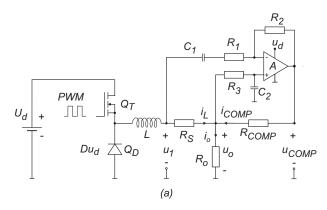

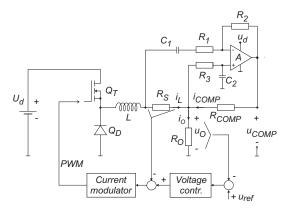

# 4 OUTPUT CURRENT-RIPPLE COMPENSATION CIRCUIT

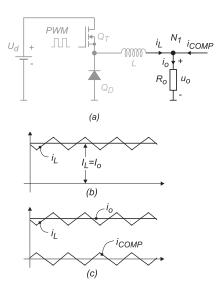

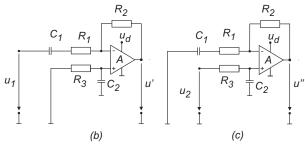

The hybrid-structured converter, consisting of a buck converter and linear amplifier is shown in Fig. 3 (a). Linear amplification is implemented, using a high-voltage/high-current operational amplifier. The shunt resistor  $R_S$ , operational amplifier, and resistor  $R_{COMP}$  form a current-controlled current source. Measurement of the inductor current ripple is obtained from sensing resistor  $R_S$  and by using a filter made of capacitor  $C_1$  and other elements, accompanied by the operational amplifier indicated by A.

Fig. 3. (a) Hybrid structured buck converter; (b) Inverting amplifier; (c) non-inverting amplifier

The voltage  $u_{COMP}(t)$  appears on the amplifier output and generates the compensation current  $i_{COMP}(t)$ . The compensation voltage  $u_{COMP}(t)$  is calculated by the use of the superposition principle.

$$u_{COMP}(t) = u'(t) + u''(t)$$

(7)

Therefore, the filter-amplifier circuit can be solved in two steps, as shown in Fig. 3 (b), (c). For further analysis (7) is transformed in the s domain. The output voltages u'(s), and u''(s) are calculated separately for each circuit, as follows:

$$u'(s) = \frac{-sR_2C_1}{sR_1C_1 + 1}u_1(s)$$

(8)

$$u''(s) = \frac{1}{sR_3C_2 + 1} \left( 1 + \frac{sR_2C_1}{sR_1C_1 + 1} \right) u_2(s)$$

(9)

and according to (7) the voltage  $u_{COMP}(s)$  is expressed by:

$$u_{COMP}(s) = \frac{u_2(s)\left(sa_1 + 1\right) - u_1(s)\left(s^2a_2 + sa_3\right)}{s^2b_1 + sb_2 + 1}$$

(10)

where  $a_1 = C_1(R_1 + R_2)$ ,  $a_2 = R_2R_3C_1C_2$ ,  $a_3 = R_2C_1$ ,  $b_1 = R_1R_3C_1C_2$  and  $b_2 = R_1C_1 + R_3C_2$ . From the

schemes in Figs. 3 (a),(b) and (c) the voltages  $u_o(s)$ ,  $u_1(s)$  and  $u_{COMP}(s)$  can be calculated as:

$$u_{o}(s) = u_{2}(s) = (i_{L}(s) + i_{COMP}(s))R_{o}$$

$$u_{1}(s) = i_{L}(s)(R_{S} + R_{o}) + i_{COMP}(s)R_{o}$$

$$u_{COMP}(s) = (i_{L}(s) + i_{COMP}(s))R_{o}$$

$$+ i_{COMP}(s)R_{COMP}$$

(11)

The current transfer function can be evaluated from (10) and (11) as follows:

$$F_{COMP}(s) = \frac{i_{COMP}(s)}{i_L(s)} = \frac{-s^2c_1 - sc_2}{s^2d_1 + sd_2 + d_3},$$

(12)

where:

$$\begin{split} c_1 &= R_3 C_1 C_2 \left( R_o \left( R_1 + R_2 \right) + R_2 R_S \right) \\ c_2 &= R_o R_3 C_2 + R_2 R_S C_1 \\ d_1 &= R_3 C_1 C_2 \left( R_o \left( R_1 + R_2 \right) + R_1 R_{COMP} \right) \\ d_2 &= R_o R_3 C_2 + R_{COMP} \left( R_1 C_1 + R_3 C_2 \right) \\ d_3 &= R_{COMP}. \end{split}$$

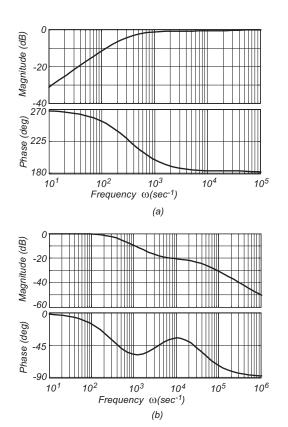

When (12) is observed along the positive imaginary axis than the frequency properties of  $F_{COMP}(s)$  is extracted as  $|F_{COMP}(j\omega)|$ , which can be obtained for all  $\omega \geq 0$ . In order to obtain the magnitude and phase frequency margin it is necessary to use instead of complex variable s only  $j\omega$  ( $s=\sigma+j\omega$ , where  $\sigma=0$ ). The Bode plot of consists of two plots: gain versus frequency and phase versus frequency. The magnitude  $A_{hf}(\omega)$  of (12) can be evaluated as:

$$A_{hf}(\omega) = |F_{COMP}(j\omega)|$$

$$= \frac{\sqrt{(-\omega^2 c_1)^2 + (\omega c_2)^2}}{\sqrt{(d_3 - \omega^2 d_1)^2 + (\omega d_2)^2}}$$

(13)

and phase margin:

$$\varphi(\omega) = \pi + \arctan \frac{c_2}{c_1 \omega} - \arctan \frac{d_2 \omega}{d_3 - d_1 \omega^2}$$

(14)

After inspection of (13), (14) and the Bode plots shown in Fig. 4(a), it is evident that the DC inductor current component is attenuated significantly while the phase of high frequency components is inverted. When  $\omega=0$ , and  $\omega=\omega_s$ , it follows that  $A_{hf}(0)\doteq 0$ ,  $(-\infty\ dB)$  and  $A_{hf}(2\pi f_s)=1$ ,  $(0\ dB)$  respectively. The phase shift  $\varphi$  of  $i_{COMP}$  is  $180^{\rm O}$  at the frequency  $\omega_s$ . Therefore, a filter with appropriate chosen parameters fulfills condition (6) during steady state operation.

The relation between the inductor and output currents is obtained from (4) and (12) as follows:

$$\frac{i_o(s)}{i_L(s)} = 1 + \frac{i_{COMP}(s)}{i_L(s)} = \frac{s^2 e_1 + s e_2 + d_3}{s^2 d_1 + s d_2 + d_3}, \quad (15)$$

Fig. 4. (a) Transfer function  $i_{COMP}(s)/i_L(s)$ ; (b) Transfer function  $i_o(s)/i_L(s)$

where:

$$e_1 = R_3 C_1 C_2 (R_1 R_{COMP} - R_2 R_S)$$

$$e_2 = R_{COMP} (R_1 C_1 + R_3 C_2) - R_2 R_S C_1.$$

If  $R_1 R_{COMP} = R_2 R_S$ , (15) is simplified to:

$$F_o(s) = \frac{i_o(s)}{i_L(s)} = \frac{se_2 + d_3}{s^2d_1 + sd_2 + d_3}.$$

(16)

The Bode plot of (16) is shown in Fig. 4 (b). The magnitude  $A_{lf}(\omega)$  can be evaluated as:

$$A_{lf}(\omega) = |F_o(j\omega)| = \frac{\sqrt{(d_3)^2 + (\omega e_2)^2}}{\sqrt{(d_3 - \omega^2 d_1)^2 + (\omega d_2)^2}}.$$

(17)

After inspection of (17) when  $\omega=0$ , and  $\omega=\omega_s$ , it follows that  $A_{lf}(0)=1$ ,  $(0\ dB)$  and  $A_{lf}(2\pi f_s)=2.24\times 10^{-2}$ ,  $(-33\ dB)$ . Therefore the output current  $i_o$  will only contain DC and the high frequency components of the inductor's current will be rejected by gain of  $-33\ dB$ .

## 5 THE PRINCIPLE VERIFICATION

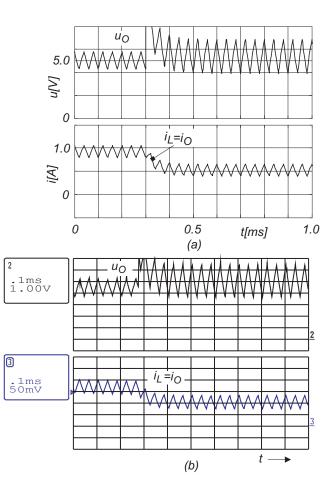

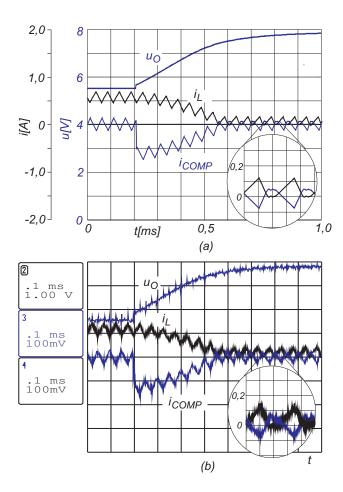

The operation of circuit shown in Fig. 3 (a) with and without proposed compensation was simulated by the

Fig. 5. (a) Simulation of an open loop operation; (b) Experiment; (x-axis  $100 \ \mu s/div$ , y-axis:  $1 \ V/div$  voltage  $u_O$ ; y-axis:  $0.25 \ A/div$ , currents  $i_L = i_O$

MATLAB-SIMPOWERSYSTEM program and afterwards was verified by experimental prototype. The continuous and discontinuous conducting mode of Buck-converter operation was considered.

# 5.1 Simulation and experiment of the Open-Loop System without Compensation (Continuous and Discontinuous Current Mode of Operation)

The simulation and experimental results for the capacitor-less buck converter, are shown in Figs. 5 (a) and (b) respectively. The inductor current's response, its ripple and output voltage's response and its ripple are as predicted by (1) and (2). The output voltage is set at 5~V by the duty cycle  $\Delta_p$ . The variables are observed in steady and transient states. At  $300~\mu s$  the load changes from  $R_o = 5~\Omega \longrightarrow 10~\Omega$ . It is evident from the voltage response that the output voltage ripple is load-dependent due to more or less constant inductor current ripple. The current and voltage ripples are as is predicted by (1) and (2).

Fig. 6. (a) Simulation; (b) Experiment; (x-axis  $100\mu s/div$ , y-axis: voltage 5V/div voltage  $u_o$ ; y-axis: 0.25A/div currents  $i_L=i_o$ )

Fig. 7. Open loop operation (a) Simulation; (b) Experiment (x-axis  $100\mu s/div$ , y-axis: 1V/div voltage  $u_o$ ; y-axis: 0.25A/div currents  $i_L=i_o$ )

The calculation of the current and voltage ripple indicated in (1) and (2) are in agreement with the simulation and experimental results shown in Figs. 5 (a) and (b). The operation of the converter in discontinuous current mode was also investigated by simulation and verified by experiment as is shown in Figs. 6 (a) and (b) respectively.

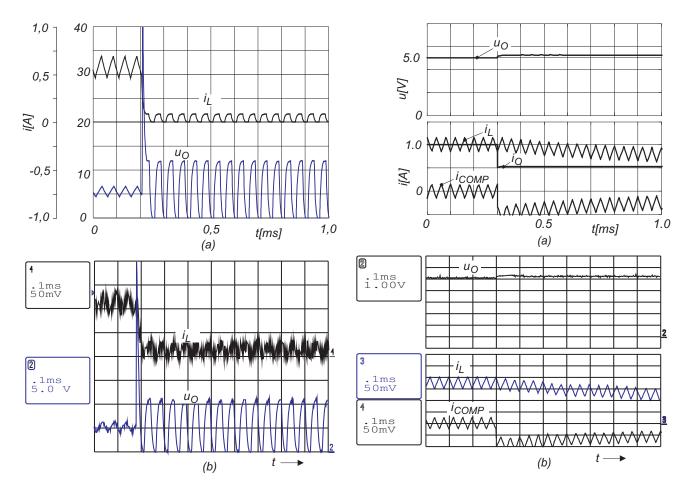

# 5.2 Simulation and experiment of the Open-Loop System with Compensation (Continuous and Discontinuous Current Mode of Operation)

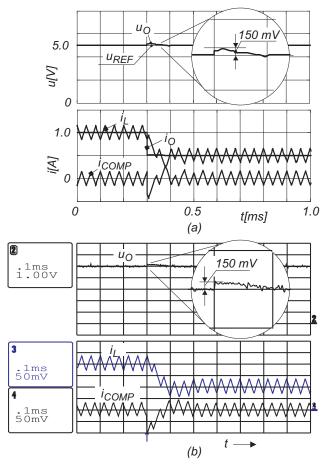

The output current ripple and, consequently, the voltage ripple is compensated for, as proposed in the section 4. The simulation and experimental results are shown in Figs. 7 (a) and (b) respectively. The simulation and experimental results were performed during transience under the same condition indicated in chapter 5.1. According to the Bode plot in Fig. 4 (b), and from (17), it is evident that the compensating voltage  $u_{COMP}$  generates the suitable current  $i_{COMP}$ , thus reducing the output voltage ripple.

The output voltage ripple can be evaluated by considering, (1),(2), and (17). It follows that the voltage ripple  $\Delta u_o$  can be estimated as:

$$\Delta u_o = |F_o(j\omega)| \, \Delta i_L R_o \tag{18}$$

The compensation principle was also investigated in discontinuous current mode of operation. It is indicated that the load step change causes the same voltage response as is known from Buck converter theory and praxis when capacitor is applied in the circuit. Figs. 8 (a) and (b) show the simulation and experimental results respectively when load was changed from  $10\Omega$  to  $180\Omega$ .

The voltage ripple, indicated by (18) is actually evaluated under the converter's steady-state operation, but according to the results in Figs 7 (a) and (b), 8 (a) and (b) the current  $i_{COMP}$  is not DC-free during the transient. Such responses cause an additional dissipation on the compensating amplifier A. A control of output variables (output voltage  $u_o$  and inductor current  $i_L$ ) need to be introduced

Fig. 8. Open loop operation DCM with the compensating circuit: (a) Simulation; (b) Experiment; (x-axis  $100\mu s/div$ , y-axis 0.5A/div: currents  $i_L$ ,  $i_{COMP}$ , y-axis 1V/div: voltage  $u_o$ )

in order to reduce the influence of this undesired phenomena. After inspection of many control principles, the current mode control is applied, as suggested in [15] and [16].

# 5.3 Output Current-Ripple Compensation and Current Mode Control; Simulation and Experiment

The current-mode control denotes the multi-loop control where the voltage loop is superior to the current-control loop. The current-mode control principle, shown in Fig. 9 was first considered by simulation and afterwards by experiment. PWM based on synchronized clock pulse and appropriate compensating ramp is applied for the current mode control as suggested in [17] and [16]. The PI controller is chosen for voltage control. The parameters of the PI controller were designed, based on the standard model received by injected-absorbed current method [15]. The operation principle is verified under the transient re-

Fig. 9. Hybrid structured buck-converter with voltage and current control loop

Fig. 10. Current-mode controlled: (a) Simulation; (b) Experiment; (x-axis  $100\mu s/div$ , y-axis: y-axis 0.25A/div: currents  $i_L$ ,  $i_{COMP}$ , y-axis 1V/div: voltage  $u_O$ )

sponse ( $R_o$  was changed from  $5~\Omega \longrightarrow 10~\Omega$ ). Fig. 10 (a) shows the currents and voltage responses. There is an expected voltage overshot during the transience. The current

mode control was applied in the buck-converter prototype based on the scheme shown in Fig. 9. The experiment was performed under the same conditions as in simulation. The measured voltage ripple in a steady state was equal to the predicted voltage ripple by (18). The current-mode controlled buck converter experimental results are shown in Fig. 10 (b). In addition, the transient behavior in the experiment was the similar as predicted by the simulation (Fig. 10 (a)).

### 5.4 Power Dissipation of Linear Amplifier

Before evaluating power dissipations, it must be noted that the prototype was initially built to demonstrate the compensation principle, therefore, the used components are not optimized to achieve minimal power dissipations. The power dissipations on the sensing resistor  $R_S$ , compensating resistor  $R_{COMP}$  and on the output stage of the linear amplifier A are calculated. To simplify the dissipation calculations, the inductor current (Fig. 11) can be expressed as: 5

$$i_{L}(t) = \begin{cases} \frac{\Delta i_{L}}{t_{on}} t - \frac{\Delta i_{L}}{2} + I_{o}, & t_{1} \leq t < t_{2} \\ \frac{-\Delta i_{L}}{T_{s} - t_{on}} t + \frac{\Delta i_{L}(T_{s} + t_{on})}{2(T_{s} - t_{on})} + I_{o}, & t_{2} \leq t < t_{3} \end{cases}$$

(19)

The power dissipation on resistors  $R_S$  and  $R_{C\!O\!M\!P}$  is calculated as:

$$P_{R_S} = \frac{R_S}{T_s} \int_0^{T_s} i_L^2(t) dt = \frac{R_S}{12} \Delta i_L^2 + I_o^2 R_S,$$

(20)

$$P_{R_{COMP}} = \frac{R_{COMP}}{T_s} \int_0^{T_s} (i_L(t) - I_o)^2 dt$$

$$= \frac{R_{COMP}}{12} \Delta i_L^2 \qquad (21)$$

The output stage of the linear amplifier, used for compensating circuits works in AB class. Fig. 12 (a) shows the scheme of the output amplifier stage. The compensation voltage  $u_{COMP}$  could be evaluated as:

$$\hat{u}_{COMP} = u_o \pm \hat{i}_{COMP} R_{COMP} \tag{22}$$

Fig. 11. The inductor current waveforms

Fig. 12. (a) Amplifier output stage; (b) The current waveforms

where  $\hat{}$  denotes the peak values of the compensating voltage and current respectively. According to the diagram in Fig. 12 (b) the current peak is  $\hat{i}_{COMP} = \Delta i_L/2$ . In order to evaluate transistor dissipation, it is convenient to use  $\hat{u}_{COMP} \doteq u_o$ . In this case, the dissipation on both transistors can be evaluated as:

$$P_A = P_{Q1} + P_{Q2} = (U_d - u_o) I_{Q1} + u_o I_{Q2},$$

(23)

where  $I_{Q1}$  and  $I_{Q2}$  are the average values of  $i_{Q1}$  and  $i_{Q2}$ . Due to the same wave-shapes' yields:

$$I_{Q1} = I_{Q2} = \frac{1}{T_s} \int_{0}^{T_s/2} i_{Q1} dt = \frac{\Delta i_L}{8}.$$

(24)

From (23) and (24) and [9] the dissipation can be calculated as:

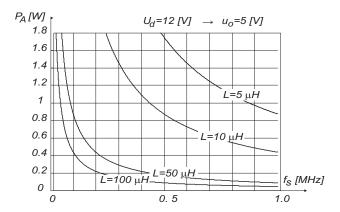

$$P_A = U_d \frac{\Delta i_L}{8} = U_d \frac{(U_d - u_o)\Delta_p}{8Lf_s}.$$

(25)

If controlled Buck converter is considered (see Fig.9) the difference between usual structure with the output capacitor and proposed structure without the output capacitor is only in the components  $R_{COMP}$  and A. Therefore the power dissipations on the compensating resistor  $R_{COMP}$ and linear amplifier A must be calculated in order to compare the efficiency between the usual Buck converter structure and the proposed structure. According to (21) and (25) in steady state the power dissipations on the resistor  $R_{COMP}$  and linear amplifier A are in direct correlation with the inductor current ripple  $\Delta i_L$ . To evaluate the power dissipations for the worst case scenario the dissipations are calculated at duty-cycle  $\Delta_p = 0.5$ , where according to (1) the inductor current ripple  $\Delta i_L$  is maximal. The calculated dissipation results and efficiency factor for the both converter structures are summarized in Table 1. The result are obtained at two different load levels, that is  $R_o = 5 \Omega$  and  $R_o = 10 \Omega$ . The efficiency factors  $\eta_1$  and  $\eta_2$

Fig. 13. Converter parameter's design diagram

for the usual Buck converter structure where an ideal coil and an ideal switch is assumed for the proposed structure are calculated as follows:

$$\eta_1 = \frac{P_o}{P_o + P_{R_s}} \tag{26}$$

$$\eta_2 = \frac{P_o}{P_o + P_{R_s} + P_{R_{COMP}} + P_A} \tag{27}$$

From the results give in Table 1, it is evident that dissipation on the compensating resistor is practically negligible, while dissipation on the sensing resistor is even grater than one of the linear amplifier in case of load  $R_o = 10 \Omega$ . Dissipation on the sensing resistor can be easily and fairly reduced by using the lower value for the sensing resistor. In this case the elements accompanying the operational amplifier must be recalculated. Relatively high dissipation on the linear amplifier which reduces the overall efficiency is the main drawback of the proposed compensating principle. This is especially true when the inductor-current ration  $(\Delta i_o/I_o)$  is above recommended level 0.3 [9], [16]. However from (25) it is evident that power dissipation on the linear amplifier depends on inductance L and the switching frequency  $f_s$  as shown in Fig. 13. So the dissipation on the linear amplifier can be minimized by appropriate

Table 1. Calculated power dissipations

| $R_o[\Omega]$     | 5     | 10    |

|-------------------|-------|-------|

| $\Delta i_L[A]$   | 0.293 | 0.293 |

| $I_o[A]$          | 1.091 | 0.571 |

| $P_o[W]$          | 5.950 | 3.265 |

| $P_{R_S}[W]$      | 0.599 | 0.167 |

| $P_{R_{COMP}}[W]$ | 0.004 | 0.004 |

| $P_A[W]$          | 0.439 | 0.439 |

| $\eta_1$          | 0.91  | 0.95  |

| $\eta_2$          | 0.85  | 0.84  |

circuit design in order to achieve the reasonable converter efficiency.

### 6 CONCLUSION

This paper deals with the low power buck converter output voltage ripple minimization by compensating the inductor current ripple by using filter based operational amplifier. The operational amplifier can be incorporated into single-chip buck converters. The additional amplifier do not occupy to much surface in the silicon. The single-chip buck converter will have the same dimension, but on the output there is no need for capacitor in order to smooth the output voltage.

Operational amplifier output transistors are designed to cover the magnitude of compensating current ripple. The compensating circuit was also capable to cover the buck-converter operation in light mode (discontinuous inductor current). The drawback of the described approach becomes evident in the case of load current step change, which implies that this principle can be used only under the closed-loop converter operations. The obtained experimental results are promising and enables the improvement of the low power single chip buck converter's applications.

### REFERENCES

- [1] J. D. van Wyk, F. C. Lee and B. Lu, "Integrating active, passive and emi-filter functions in power electronics systems: A case study of some technologies," *IEEE Transaction on Power Electronics*, vol. 20, no. 3, pp. 523–536, 2005.

- [2] J. Popovic and J. A. Ferreira, "An approach to deal with packaging in power electronics," *IEEE Transaction on Power Electronics*, vol. 20, no. 3, pp. 550–557, 2005.

- [3] F. Mihalic and D. Kos, "Reduced conductive emi in switched-mode dc-dc power converters without emf filters: Pwm versus randomized pwm," *IEEE Transaction on Power Electronics*, vol. 21, no. 6, pp. 1783–1794, 2006.

- [4] F. C. Lee, J. D. van Wyk, T. Jahns, R. D. Lorenz, T. P. Chow, R. Gutmann and P. Barbosa, "An Integrated Approach to Power Electronics System," *Automatika, Journal for Control, Measurement, Electronics, comuting and comunnications*, vol. 44, no.1-2, pp. 5–20, 2003.

- [5] L. Corradini, P. Mattavelli and D. Trevisan, "High-bandwidth multisampled digitally controlled dc-dc converters using ripple compensation," *IEEE Transaction on Industrial Electronics*, Vol. 55, No. 4, April 2008.

- [6] A. Šabanovič, N. Šabanovič and K. Jezernik, "Sliding Mode in Sampled Data System," *IEEE Automatika, Jour*nal for Control, Measurement, Electronics, comuting and comunications, vol. 44, no.3-4, pp. 163–181, 2003.

- [7] T. Senanayake and T. Ninomiya, "Improved topology of inductor-switching *dc-dc* converter," *IEEE Transaction on Industrial Electronics*, vol. 52, no. 3, 2005.

- [8] X. Du and H. Tai, "Double-frequency buck converter," IEEE Transaction on Industrial Electronics, vol. 56, no. 5, 2009.

- [9] N. Mohan, T. Undeland, Power Electronics, Devices, Converter, Application and Design. New York, Singapore, Toronto, Brisbane: John Wiley and Sons, 1989.

- [10] M. Zhu, D. J. Perreault and J. Kassakian, "Design and evaluation on feedforward active ripple filters," *IEEE Trans*action on Power Electronics, vol. 20, no. 2, pp. 276–285, 2005.

- [11] K. I. Hwu and Y. Yau, "Two types of ky buck-boost converters," *IEEE Transactions On Industrial Electronics*, vol. 56, no. 8, 2010.

- [12] G. R. Walker, "A class b switch-mode assisted linear amplifier," *IEEE Transaction on Power Electronics*, vol. 18, no. 6, pp. 1278–1285, 2003.

- [13] A. E. Ginart, R. M. Bass and T. G. Habetler, "Analysis of the class ad audio amplifier including hysteresis effects," *IEEE Transaction on Power Electronics*, vol. 18, no. 2, pp. 679–685, 2003.

- [14] E. Vidal-Idiarte, L. Martinez-Salamero and A.Romero, "An H<sub>∞</sub> control strategy for switching converters in sliding-mode current control," *IEEE Transaction on Power Electronics*, vol. 21, no. 2, pp. 553–556, 2006.

- [15] A.S. Kislovski, R. Redl, Dynamic Analysis of Switching-Mode DC/DC Converters. New York: Van Nostrand Reinhold, 1991

- [16] R.W. Ericson, Fundamentals of Power Electronicss. New York: Norwell, Mass., Kluwer Academic, 2001.

- [17] B. Bryant and M. K. Kazimierczuk, "Voltage-loop powerstage transfer functions with mosfet delay for boost pwm converter operating in ccm," *IEEE Transaction on Industrial Electronics*, vol. 21, no. 2, pp. 553–556, 2006.

Aljaž Kapun received the B.Sc. and Ph.D. degrees in electrical engineering from the University of Maribor, Maribor, Slovenia, in 2003 and 2009 respectively. Since 2009 he is employed at EXOR-ETI d.o.o. company where he is working as head developer on the small battery electric vehicle project.

Mitja Truntič received the B.Sc. and Ph.D. degrees in electrical engineering from the University of Maribor, Maribor, Slovenia in 2004, and 2009, respectively. Since 2009, he has been working as Senior Researcher at University of Maribor, Faculty of Electrical Engineering and Computer Sciences, Slovenia. His research interests are in the field of R&D work dealing with design and development of power electronic devices, and implementation of control algorithms into field programmable gate array.

Alenka Hren received the B.Sc. degree in 1987, the M. Sc. degree in 1990 and the D. Sc in 2000, all in electrical engineering from the University of Maribor, Slovenia. From 1987 to 1994 she worked as a researcher at the Faculty of Electrical Engineering and Computer Science, University of Maribor. Since 1994 she has been working as a teaching assistant at the same institution. In 1990 she spent six months as a visiting research student at the Imperial College, London, England. She was awarded by the Slovenian Ministry of

Science and Technology and ISKRA Holding with the Bedjanic award for master thesis. Her research interests are in the field of power electronics, modeling and control of dc-dc converters, control of electrical drives and estimation techniques.

Miro Milanovič received the B.Sc., M.Sc. and the doctorate degrees in electrical engineering from the University of Maribor, Maribor, Slovenia in 1978, 1984, and 1987, respectively. From 1978 to 1981 he worked as a Power Electronics Research Engineer at TSN Co. Maribor, Slovenia. From 1981 to the present he has been a Faculty member of the Faculty of Electrical Engineering and Computer Sciences, University of Maribor, Slovenia. In 1993 he was a visiting

scholar at the University of Wisconsin, Madison,

USA and in 1999 he spent two months at the University of Tarragona, Spain as a visiting professor. Currently he has a full professor position at the University of Maribor. His main research interests include control of power electronics circuits, unity power factor correction and switching matrix converters. Dr. Miro Milanovic served as vice-president of the Slovenian IEEE section in the period 2002-2006.

AUTHORS' ADDRESSES

Aljaž Kapun, Ph.D.

EXOR ETI d.o.o.

Stegne 7, 1000, Ljubljana, Slovenia

email: aljaz.kapun@exor-eti.si

Mitja Truntič, Ph.D.

Asst. Prof. Alenka Hren, Ph.D.

Prof. Miro Milanovič, Ph.D.

University of Maribor,

Faculty of electrical engineering and computer sciences,

Smetanova 17, 2000, Maribor, Slovenia

email: mitja.truntic@uni-mb.si, alenka.hren@uni-mb.si

milanovic@uni-mb.si

Received: 2011-04-18 Accepted: 2011-12-08