# FCS-MPC Control Strategy for a New Fault Tolerant Three-level Inverter

DOI 10.7305/automatika.2017.02.1293 UDK [681.518.25.07-047.58:621.314.5.072.2.049]:629.7.067

Original scientific paper

In order to meet the high reliability of aviation inverters, the paper established a new three-level inverter which can increase the reliability in safety-critical applications, what's more, the new topology adding assistant leg to control neutral-point voltage independently. On the basis of the new topology, a mixed logic dynamic (MLD) model was established for the new inverter circuits, and takes finite control set model predictive control (FCS-MPC) for the new inverter. The method takes a discrete-time model of inverter to predict the future value of the all possible voltage vectors generated by the inverter. The vector which minimizes objective function in finite control set is selected as the control of inverter, the objective function used in this work evaluates the voltage error and the switch frequency at the next sampling time. The paper explicitly researched the solving algorithm and realization procedure of the new inverter circuit, its feasibility and validity is verified by the experiment.

Key words: Three-level inverter, Fault tolerant, Model predictive control, Mixed logic dynamic model

FCS-MPC upravljačka strategija novim trorazinskim izmjenjivačem otpornim na kvarove. Za postizanje visokog stupnja pouzdanosti avijacijskih izmjenjivača, u radu je postavljena nova topologija trorazinskog izmjenjivača za primjene u sigurnosno kritičnim sustavima koja ima dodatnu pomoćnu granu za nezavisno upravljanje naponom neutralne točke. Zasnivajući se na ovoj novoj topologiji, dinamički model s mješovitom logikom (MLD) postavljen je za električne krugove novog ispravljača koji za upravljanje pretvaračem koriste konačni skup upravljačkih signala dobivenih modelskog prediktivnog upravljanja (FCS-MPC). Metoda koristi vremenski diskretni model izmjenjivača za predviđanje budućih vrijednosti svih mogućih vektora napona koje generira izmjenjivač. Za upravljanje pretvaračem koristi se upravljački vektor iz konačnog skupa upravljačkih signala dobiven minimiziranjem funkcije cilja koja u obzir uzima grešku napona i frekvenciju sklapanja u sljedećem koraku diskretizacije. U radu je izravno razvijen algoritam za rješavanje problema i procedura za realizaciju nove topologije izmjenjivača, a izvedivost i validnost provjereni su eksperimentalno.

Ključne riječi: Trorazinski izmjenjivač, otpornost na kvarove, modelsko prediktivno upravljanje, dinamički model mješovite logike

#### **1 INTRODUCTION**

In recent years, the use of three-level inverters has increased during the last years in many application such as distributed generation, energy storage systems and uninterruptible power supply, due to lower harmonics of output voltage and current at same switching frequency compared to 2-level inverter[1-2]. However, the inverter still exist some problems, firstly, the unbalance of neutral point across the dc-link will generate order harmonic in output[3], a modulation strategy was proposed in [4] which ensures that the average neutral-point current within a switching period is equal to zero,. However, the nonidealities of the components, transients, etc., may cause the neutral-point voltage variation. Therefore, a closed loop controller is required to maintain the neutral-point voltage balance. The controllers proposed in [5] are based on nonlinear discontinuous model of the neutral-point voltage dynamics. This makes the controller design difficult. In [6] presents a four-leg hybrid converter, the fourth leg provides a reliable NP voltage under normal operation mode, However, when the fourth legs take the replacement of the fault phase, the NP voltage have to handle by the adjustment of control algorithm.

Secondly, since three-level inverters have a large number of semiconductor devices, which implies an increase in the number of components when compared with twolevel inverter. This in turn brings a higher fault probability with a consequent reliability reduction, since any device failure may cause the inverter abnormal operation and economic losses [7], so improving the reliability is important to the continuous drive operation, one commonly practiced method is improving tolerance control [8][9] of the inverter, which may result in a degraded operation of the system, another way is made the inverter are operated in parallel to get the redundant operation [10]. In general, the new topologies of the three-level inverter should be researched.

Finite Control Set Model Predictive Control (FCS-MPC) is a sort of control strategy that can be applied for the control of power inverters, it makes use of the discrete finite number of switching states and the non-linear nature of the inverters, by the minimization of a objective function, which contains the goals, can be achieved by predicting the next output in the finite set of the switching states [11], it is widely used to control power electronic inverters. This technique has been successfully tested in [12],[13].

This paper presents a new solution to achieving faulttolerant ability with the new three-level inverter and by adding an assistant leg to control neutral-point voltage independently to solve the control problem of neutral-point voltage.

In Section 2, an mixed logical dynamical (MLD) model for the new inverter model is founded. The three-level inverters which include discrete events in the differential equations are typical hybrid system, MLD model is one of the modeling methods of hybrid system [14], which takes the total system as a differential equation, so a MLD model could be founded in order to research the control of the new inverter. In Section 3 the FCS-MPC method of a new inverter based on MLD model is researched. In Section 4, the simulation and experiment are presented.

### 2 MATHEMATICAL MODEL OF INVERTER

#### 2.1 The operation of new inverter

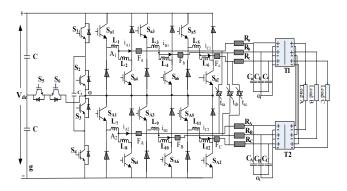

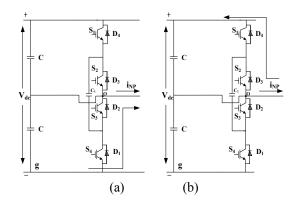

The new inverter topology is shown at Fig. 1, it consists in two symmetrical two-level inverters in series by transformers  $T_1$  and  $T_2$ , switches  $S_1 - S_6$  add to balance the voltage of neutral point O, the inverter output voltages have high order harmonic components due to the switching of the power semiconductors. Thus the inverter is connected to the load through a LC filter in order to provide a high quality sinusoidal voltage.

The switch states of A phase of inverter is shown in Tab. 1, similarly to the rest two phases,  $U_{A_{1g}}$  is voltage between  $A_1$  and g,  $U_{A_{2g}}$  is voltage between  $A_2$  and g,  $r_1 - r_6$  are control signals of switch  $S_{a1} - S_{a6}$ ,  $r_7 - r_{12}$  are control signals of switch  $S_{A1} - S_{A6}$ .

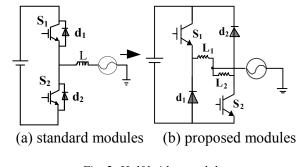

In the new inverter, the special connection of the halfbridge modules was put forward as show in Fig. 2(b). The standard inverter unit in Fig. 2(a) is decompose into two bridge legs, when the two switches  $S_1$ ,  $S_2$  are conducted

Fig. 1. New inverter topology

Fig. 2. Half bridge module

at the same time, the diodes  $d_1$ ,  $d_2$  can stop the short current, so the new modules guarantees that the shoot-through problem does not exist in the proposed topology, in this way, the dead time between the switches need not be set, the waveform quality of the voltage can be improved.

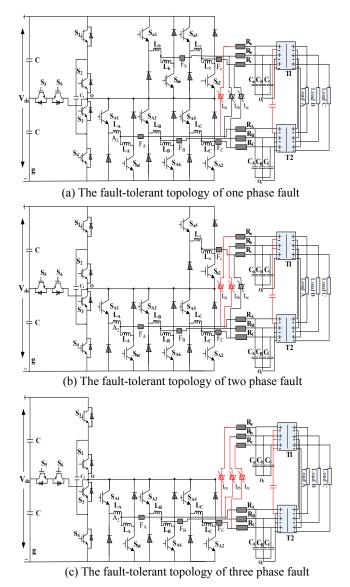

Within a three-level voltage source inverter, the probability of a failure in these devices is higher and must be therefore to be taken into account. Several factors can cause failures, such as transistor short-circuit and transistor open-circuit. The original NPC topology was changed by applying symmetry structure of two-level inverters. Obviously, the proposed topology has the additional redundancy to solve the semiconductors fault problems, as an example, suppose that an open-circuit failure of the *Sa1* power switch (phase A) while the inverter is supplying a three-phase nonlinear load, first step with some additional fast fuses connecting the failure leg to the symmetry halfbridge in order to realize continuous work as traditional two-level inverters (in Fig. 3(a))., in addition, it is nec-

| Table 1. Switch states of A phase  |                        |  |  |  |  |  |

|------------------------------------|------------------------|--|--|--|--|--|

| $(S_{a1}, S_{a4}, S_{a1}, S_{a4})$ | $(U_{A_1g}, U_{A_2g})$ |  |  |  |  |  |

| (1,0,1,0)                          | $(V_{dc}, V_{dc}/2)$   |  |  |  |  |  |

| (0,1,0,1)                          | $(V_{dc}/2, 0)$        |  |  |  |  |  |

| (0,1,1,0)                          | $(V_{dc}/2, V_{dc}/2)$ |  |  |  |  |  |

| (1,0,0,1)                          | $(V_{dc}, 0)$          |  |  |  |  |  |

essary to connect the negative of the faulty output to the output of the symmetry leg. A similar process can be performed to two-phase fault Fig. 3(b) and three-phase fault Fig. 3(c), so the rest of the phases will be able to continue operating as two-level inverters normally.

Fig. 3. The inverter of fault events

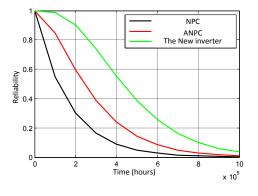

To evaluate and compare the reliability of ANPC[15], NPC, and the new inverters, the inverter reliability is analyzed for a general purpose rather than an accurate reliability engineering calculation, therefore, some factors, such as quality factor, stress factor and temperatures factor are not considered. According to MIL-HDBK-217F military standard, the calculation method of reliability function of the device is show in literature [15] in detail.

The results in Fig. 4 show that the new inverter has

Fig. 4. Reliability with ANPC and NPC inverters

higher reliability compared to ANPC and NPC inverters for multiple failure applications.

#### 2.2 MLD model

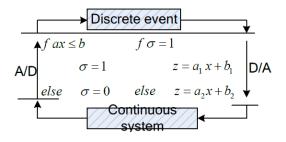

MLD system can be viewed as a collection of systems of various types. A hierarchical structure arises when a logical control unit governs such a system by issuing logic decisions, this leads to the system framework shown in Fig. 5 which clearly illustrates this architecture. The top layer is a discrete event system, the bottom layer is a continuous system, the interface plays the role of facilitating communication between the two different layer by means of translating signals between them [16][17].

Fig. 5. MLD Structure Diagram

Each combination of switch state of inverter is defined as one discrete event, and each change of switch state will cause the inverter transforming from initial discrete event to objective discrete event.

For the inverter is symmetrical structures, the paper take phase A as an example, similarly to the rest two phases. As shown in Fig. 1, phase A of the inverter which form by the upper half-bridge  $A_1$  and the lower half-bridge  $A_2$ , The switch states of phase A is shown in Tab. 1. The value of  $r_1 - r_6$  are "1" or "0", and "1" means on, "0" means off, right is the positive direction of current  $i_{A1}$ , the working state of the upper half-bridge of phase A is shown as (1), similar way to the lower half-bridge.

$$\begin{array}{ll} \text{when} & i_{A1} > 0 \\ & \text{if} \ r_1 = 0, r_4 = 1, \text{then}, u_{A_1g} = V_{dc}/2, \\ & \text{if} \ r_1 = 1, r_4 = 0, \text{then}, u_{A_1g} = V_{dc}, \\ & \text{if} \ r_1 = 0, r_4 = 0, \text{then}, u_{A_1g} = V_{dc}/2, \\ & \text{when} \ i_{A1} < 0 \\ & \text{if} \ r_1 = 0, r_4 = 1, \text{then}, u_{A_1g} = V_{dc}/2, \\ & \text{if} \ r_1 = 1, r_4 = 0, \text{then}, u_{A_1g} = V_{dc}, \\ & \text{if} \ r_1 = 0, r_4 = 0, \text{then}, u_{A_1g} = V_{dc}, \\ & \text{if} \ r_1 = 0, r_4 = 0, \text{then}, u_{A_1g} = V_{dc}, \\ & \text{if} \ r_1 = 0, r_4 = 0, \text{then}, u_{A_1g} = V_{dc}, \end{array}$$

Replacing discrete event  $i_{A1} > 0$  and  $i_{A1} < 0$  with logical variable  $\sigma_{A_1} = 1$  and  $\sigma_{A_1} = 0$ , "-" means "not". The mathematical expression of voltage  $u_{A_1g}$  is shown as (2), based on the logical relation in (1).

$$u_{A_{1}g} = V_{dc} \left[ \bar{r}_{4} (r_{1} + \bar{r}_{1}\bar{\sigma}_{A_{1}}) + \frac{1}{2} \overline{\bar{r}_{4} (r_{1} + \bar{r}_{1}\bar{\sigma}_{A_{1}})} \right].$$

(2)

The MLD model of the upper half-bridge of three phases can be shown as:

$$\begin{cases} u_{A_{1}g} = V_{dc} \begin{bmatrix} \bar{r}_{4}(r_{1} + \bar{r}_{1}\bar{\sigma}_{A_{1}}) + \frac{1}{2}\overline{\bar{r}_{4}(r_{1} + \bar{r}_{1}\bar{\sigma}_{A_{1}})} \\ u_{B_{1}g} = V_{dc} \end{bmatrix} \begin{bmatrix} \bar{r}_{6}(r_{3} + \bar{r}_{3}\bar{\sigma}_{B_{1}}) + \frac{1}{2}\overline{\bar{r}_{6}(r_{3} + \bar{r}_{3}\bar{\sigma}_{B_{1}})} \\ u_{C_{1}g} = V_{dc} \begin{bmatrix} \bar{r}_{2}(r_{5} + \bar{r}_{5}\bar{\sigma}_{C_{1}}) + \frac{1}{2}\overline{\bar{r}_{2}(r_{5} + \bar{r}_{5}\bar{\sigma}_{C_{1}})} \end{bmatrix} \end{cases} .$$

$$(3)$$

The relations between  $u_{A_1g}$  and  $u_{A_1O_1}$ ,  $u_{B_1g}$  and  $u_{B_1O_1}$ ,  $u_{C_1g}$  and  $u_{C_1O_1}$  are shown in (4), where  $u_{A_1O_1}$  means the voltages between point AI and neutral point  $O_1$ ,  $u_{B_1O_1}$  means the voltages between point  $B_1$  and neutral point  $O_1$ ,  $u_{C_1O_1}$  means the voltages between point  $C_1$  and neutral point  $O_1$ .

$$\begin{cases}

u_{A_1O_1} = u_{A_1g} - u_{O_1g} \\

u_{B_1O_1} = u_{B_1g} - u_{O_1g} \\

u_{C_1O_1} = u_{C_1g} - u_{O_1g}

\end{cases}$$

(4)

In (4),  $u_{O_1g}$  means the voltage between neutral point  $O_1$  and zero voltage point g, of which the expression is shown as (5):

$$u_{O_1g} = \frac{1}{3} \left( u_{A_1g} + u_{B_1g} + u_{C_1g} \right).$$

(5)

The discrete input vector of phaseA1, B1, C1 can be shown as (6):

$$\begin{bmatrix} u_{A_1O_1} \\ u_{B_1O_1} \\ u_{C_1O_1} \end{bmatrix} = \frac{V_{dc}}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \times \\ \times \begin{bmatrix} \bar{r}_4(r_1 + \bar{r}_1\bar{\sigma}_{A_1}) + \frac{1}{2}\overline{\bar{r}_4(r_1 + \bar{r}_1\bar{\sigma}_{A_1})} \\ \bar{r}_6(r_3 + \bar{r}_3\bar{\sigma}_{B_1}) + \frac{1}{2}\overline{\bar{r}_6(r_3 + \bar{r}_3\bar{\sigma}_{B_1})} \\ \bar{r}_2(r_5 + \bar{r}_5\bar{\sigma}_{C_1}) + \frac{1}{2}\overline{\bar{r}_2(r_5 + \bar{r}_5\bar{\sigma}_{C_1})} \end{bmatrix}.$$

(6)

In a similar way, the MLD model of the lower half-

bridge of the three phases can be shown as:

$$u_{A_{2}g} = V_{dc} \left[ \frac{1}{2} \bar{r}_{10} (r_{7} + \bar{r}_{7} \bar{\sigma}_{A_{2}}) \right],$$

$$u_{B_{2}g} = V_{dc} \left[ \frac{1}{2} \bar{r}_{12} (r_{9} + \bar{r}_{9} \bar{\sigma}_{B_{2}}) \right],$$

$$u_{C_{2}g} = V_{dc} \left[ \frac{1}{2} \bar{r}_{8} (r_{11} + \bar{r}_{11} \bar{\sigma}_{C_{2}}) \right].$$

(7)

The discrete input vector of phase  $A_2$ ,  $B_2$ ,  $C_2$  can be shown as (8):

$$\begin{bmatrix} u_{A_2O_2} \\ u_{B_2O_2} \\ u_{C_2O_2} \end{bmatrix} = \frac{V_{dc}}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \times \\ \times \frac{1}{2} \begin{bmatrix} \bar{r}_{10}(r_7 + \bar{r}_7 \bar{\sigma}_{A_2}) \\ \bar{r}_{12}(r_9 + \bar{r}_9 \bar{\sigma}_{B_2}) \\ \bar{r}_8(r_{11} + \bar{r}_{11} \bar{\sigma}_{C_2}) \end{bmatrix}.$$

(8)

The output of the voltage of each phase equal to the summation of the upper half-bridge and the lower half-bridge:

$$\begin{cases}

U_A = u_{A_1O_1} + u_{A_2O_2} \\

U_B = u_{B_1O_1} + u_{B_2O_2} \\

U_C = u_{C_1O_1} + u_{C_2O_2}

\end{cases}$$

(9)

Then, the discrete input vector of phase A, B, C in (9) is transformed to the expression of vector space by the transformation shown in (10):

$$U_{out} = \frac{2}{3} \left( U_A + \alpha U_B + \alpha^2 U_C \right), \qquad (10)$$

where  $\alpha = e^{j(2\pi/3)}$ . Similarly, transforming three phase inductor currents  $i_f$ , three phase capacitor voltages  $u_c$ , three phase output currents $i_0$  to the expressions of vector space, shown in (11):

$$\begin{cases} i_f = \frac{2}{3} \left( i_{Af} + \alpha i_{Bf} + \alpha^2 i_{Cf} \right) \\ u_c = \frac{2}{3} \left( u_{Ac} + \alpha u_{Bc} + \alpha^2 u_{Cc} \right) \\ i_0 = \frac{2}{3} \left( i_{A0} + \alpha i_{B0} + \alpha^2 i_{C0} \right) \end{cases}$$

(11)

The dynamic performance of inductors and capacitors of inverter are respectively shown in (12) and (13):

$$\frac{di_f}{dt} = \frac{1}{L} \left( U_{out} - u_c \right), \tag{12}$$

$$\frac{du_c}{dt} = \frac{1}{C} \left( i_f - i_0 \right). \tag{13}$$

Then, the MLD model of inverter can be shown as (14):

$$\dot{x} = Ax + B_1 U_{out} + B_2 i_0,$$

$$y = Dx,$$

(14)

where

$$x = \begin{bmatrix} i_f \\ u_c \end{bmatrix}, A = \begin{bmatrix} 0 & -\frac{1}{L} \\ \frac{1}{C} & 0 \end{bmatrix}, B_1 = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix}$$

$$B_2 = \begin{bmatrix} 0 \\ -\frac{1}{C} \end{bmatrix}, D = \begin{bmatrix} 0 & 1 \end{bmatrix}.$$

The prediction model of inverter based on MLD model is shown in (15), which was obtained by the discretization of (14):

$$\begin{aligned} x(k+1) &= A^* x(k) + B_1^* u_n(k) + B_2^* i_0(k), \\ y(k) &= D x(k), \end{aligned}$$

(15)

where  $A^* = e^{AT_s}$ ,  $B_1^* = \int_0^{T_s} e^{At} B_1 dt$ ,  $B_2^* = \int_0^{T_s} e^{At} B_2 dt$ .

# 2.3 The prediction model of reference output

In the proposed predictive algorithm, (15) is evaluated for each possible voltage vectors, giving different current predictions. The error between the voltage vector whose voltage prediction output and reference output should be close to zero, but the future reference value  $u_c^*(k+1)$ is unknown. So it has to be predicted from the present and previous values, the reference output will be obtained by the second order Lagrange extrapolation formula [18], which is adopted in this paper, and shown in (16):

$$u_{c}^{*}(k+1) = 3u_{c}^{*}(k) - 3u_{c}^{*}(k-1) + u_{c}^{*}(k-2).$$

(16)

#### **3** FCS-MPC OF THE INVERTER

### 3.1 Control of The Additional Leg

An important issue for multilevel inverters is the neutral point balancing, in order to balance the neutral point we need control the redundant leg. Before the in new inverter start to work, the voltage of the dc link capacitor C1 should be stable at around one half of the dc-link voltage.

In order to reduce the number of switching events in the fourth leg, the strategy shown in Table 2 is proposed. In this case, the state of the switches is determined in accordance with the voltage in the capacitor, the output currents, and the interval (or duty cycle) at which the output phases are connected to the NP. Then the variables of neutral voltage and current deviation are given as follows:

$$\Delta U = V_{dc}/2 - U_{c1},$$

$$i_{NP} = d_{s_{a4}}i_{s_{a4}} + d_{s_{a6}}i_{s_{a6}} + d_{s_{a2}}i_{s_{a2}} + d_{s_{a4}}i_{s_{a4}} + s_{a4}d_{s_{a6}}i_{s_{a6}} + d_{s_{a2}}i_{s_{a2}},$$

(17)

where,  $d_{sx}$  is the duty cycle of IGBT which is connected to the natural point O in a sampling cycle, and  $i_{NP}$  is the locally averaged NP current.

Nevertheless, there still exist some problems that may occur in the switching process of the fourth leg, the following conditions are used to for in-depth analysis.

- If S2 and S4 are activated, the switching state will be known as "state A."

- If S1 and S3 are activated, the switching state will be known as "state B."

| Table 2. Selection of the Proper State |              |           |              |  |  |  |  |  |

|----------------------------------------|--------------|-----------|--------------|--|--|--|--|--|

| $\Delta U > 0$                         | $i_{NP} > 0$ | Action    | $C_1$ states |  |  |  |  |  |

| 1                                      | 1            | $B \to A$ | Discharge    |  |  |  |  |  |

| 1                                      | 0            | $A \to B$ | Discharge    |  |  |  |  |  |

| 0                                      | 1            | $A \to B$ | Charge       |  |  |  |  |  |

| 0                                      | 0            | $B \to A$ | Charge       |  |  |  |  |  |

If the current flowing through the NP  $i_{NP}$  is positive when switching occurs in the fourth leg, this current will flow through the  $D_1$  and  $D_2$  diodes as soon as  $S_2$  is deactivated, meaning that a low voltage level will be obtained in the NP (Fig. 6(a)).

On the other hand, the current flowing through the neutral point  $i_{NP}$  is negative when switching occurs in the fourth leg, this current will flow through diodes  $D_3$  and  $D_4$  as soon as  $S_4$  is deactivated, and a high voltage level will be obtained at the NP (Fig. 6(b)). It can be observed how the voltage through the NP may temporarily vary between the high and low voltage levels, depending on the direction of the current flowing through this point. These glitches introduce certain harmonic distortion in the output voltages generated.

Fig. 6. Fourth-leg switching process between states "A" and "B" when (a)  $i_{NP}$  is positive and (b)  $i_{NP}$  is negative

Table 3 in Appendix outlines the switching sequences of the modified fourth leg shown in the inverter of Fig. 1. The conditions followed are the same as that used in Table 2. With this sequence, the voltage at the NP is always equal to  $V_{dc}/2$ , which means that the risk of glitches in the voltage waveform will be eliminated.

#### 3.2 The choice of objective function

The transformation from three-phase static voltage A, B, C to two phase static  $\alpha\beta$  is called Clarke static transformation. The transformation equations can be expressed as:

$$X_{\alpha\beta} = T_{ABC/\alpha\beta} X_{ABC},\tag{18}$$

where,

$$T_{ABC/\alpha\beta} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & \sqrt{3}/2 & -\sqrt{3}/2 \end{bmatrix}.$$

(19)

The relationship between  $U_{\alpha}$ ,  $U_{\beta}$  and  $U_A$ ,  $U_B$ ,  $U_C$  is as follows:

$$\begin{bmatrix} U_{\alpha} & U_{\beta} \end{bmatrix}^{T} = T_{ABC/\alpha\beta} \begin{bmatrix} U_{A} & U_{B} & U_{C} \end{bmatrix}^{T}.$$

(20)

Three-level inverter has 27 voltage vectors [19][20], which are used to design FCS-MPC for inverter. In order to choose a optimal voltage vector to control inverter, firstly, the values of  $U_c(k+1)$  of 27 vectors are respectively computed according to expression (15). The choice of the optimal-model-based vector system may require high computational resources and high-speed real-time digital control systems, this paper adopts a new predictive control method [21], which uses the model equations of the system just once in each control cycle to predict the ideal optimal vector needed to control the state space variables. The choice of the converter output vector is obtained by minimizing the distance between the ideal vector and the converter available vectors, the vector corresponding minimal value of distance is selected as the control signals of inverter[22].

In this paper the new inverter is operated as a voltage source, three independent variables can be controlled – two ac line voltages  $U_{\alpha}(t)$  and  $U_{\beta}(t)$ . The main objective of the optimizing controller must be the minimization of the ac line voltage errors, thus a linear or  $l_1$ -norm cost function can be set up in (21):

$$J = |U_{\alpha}^{*} - U_{\alpha}(k+1)| + |U_{\beta}^{*} - U_{\beta}(k+1)|, \quad (21)$$

where  $U_{\alpha}^{*}$  is real part of output voltage of reference,  $U_{\beta}^{*}$  is imaginary part of output voltage of reference,  $U_{\alpha}^{*}$  is real part of predictive voltage,  $U_{\beta}^{*}$  is imaginary part of predictive voltage.

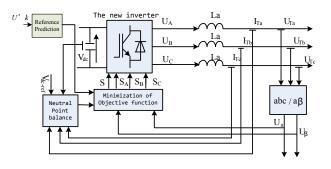

#### 3.3 The structure diagram of control strategy

A block diagram of the proposed method applied to the voltage control for the new inverter is shown in Fig. 7.

The main functions realized by Fig. 7 are listed as followings:

M. Lin, Y.-H. Li, N. Li, C. Wu, J.-B. Gao

Fig. 7. The block diagram of FCS-MPC

- 1) The prediction module forecasts reference voltage of reference at next time using (16), and the results are sent to the module of objective function.

- 2) The prediction module forecasts the output voltage of inverter using (15). However, in the experimental verification, the delay provided by the digital signal processor and switching devices is inevitable[23], so it must be compensated. In an easy way, the delay provided by the digital signal processor can be compensated by calculating the cost function at the end of the next sampling period  $U_c(k + 2)$ .

- 3) The current  $i_{NP}$  is computed by the expression of (17) using voltage of capacitor  $C_1$ .

- 4) The switch state, which minimizes the value of expression (21), is selected by the module of objective function as the control of inverter. This process is applied to every possible voltage vector generated by the inverter.

# 4 SIMULATION AND EXPERIMENT VERIFICA-TION

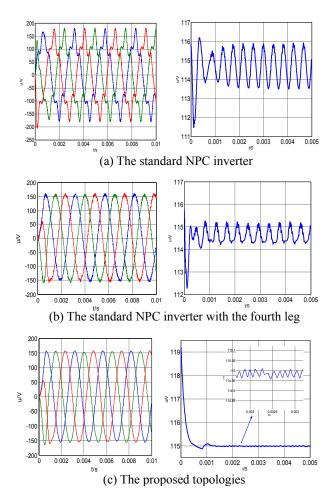

With topology of the new inverter in Fig. 1, the proposed control strategy is verified according to simulation based on MATLAB/SIMULINK, the parameters of simulation are shown as followings,  $V_{dc} = 270$ V,  $L_1 = L_2 = \cdots L_{12} = 2$ mH,  $C_a = C_b = C_c = C_A = C_B = C_C = 40\mu$ F,  $C_1 = 8800\mu$ F,  $R_a = R_b = R_c = R_A = R_B = R_C = 25$ m $\Omega$ , sampling period  $T_s$  is 10 $\mu$ s, f means rated frequency is 400Hz. The fourth leg commutates alternating its state at every sampling cycle.

Fig. 8(a) shows voltage waveforms from the standard NPC inverter operate under a nonlinear load, the system becomes unstable. These wave-forms are show in Fig. 8(b), note that with the fourth leg the improved NPC inverter can reduce the low-frequency NP voltage oscillation. Whereas, in Fig. 8(c) the same load is connected to the proposed inverter, observing that the low frequency voltage oscillation in the NP is removed, and there are practically no glitches

Fig. 8. Voltage waveforms and neutral Voltage for inverter over an nonlinear load

in the generated voltage waveforms, so the quality of these voltages is maximum attainable.

Simulation are carried out to confirm the fault tolerant of the proposed topology, Fig. 9(a) shows that the one phase fault in Sa1, it can be compute the three phase voltage THD (Total Harmonic Distortion)are 4.02%. So it can meet the demand of aviation requirement (THD<5%). Fig. 9(b) and (c) shows the results obtained when a two phase and three phase faults are happened to the topology of Fig. 1, respectively, from the results the voltage THD is acceptable to the standard.

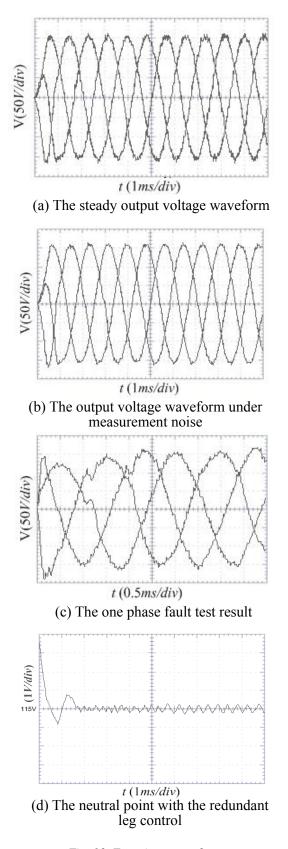

An experimental setup was developed using a DSP model TMS320C6713 for a sampling time  $T_s = 10\mu s$ , the operating conditions are given as follows:  $V_{dc} = 270$ V, L = 2mH,  $C = 40\mu$ F. Fig. 10(a) shows the voltage waveform obtained with the traditional fourth leg prototype under the nonlinear load conditions THD=2.96%, it can be observed the certain glitches appear in the output voltage waveform. As mentioned in the Section 3, this is due to

Fig. 9. Simulation result of the faults

the deadtimes allowed for the proper operation of the IG-BTs of the fourth leg. On the other hand, Fig. 10(b) shows the output voltages waveform of the proposed topology, THD=1.74%. When the fault occurs in phase A1, the fault tolerant ability is shown in Fig. 10(c), THD=4.58%. At last the result of neutral point voltage control is given in Fig. 10(d).

# 5 CONCLUSION

200 150 100

This paper presents a new approach to the three-level inverter in terms of fault-tolerance, the new inverter combined with an additional leg to control neutral-point voltage independently. On the basis of the new topology, a MLD model of inverter has been set up, and the model is used as the prediction model to research FCS-MPC for inverter, which guarantees well steady state characteristics and transient characteristics of inverter, the quality of output voltages has been also improved, in addition, the new topology combines with two-level inverter control tech-

Fig. 10. Experiment results

nique ensures the fault-tolerance to multiple failure modes of the semiconductors, the feasibility and effectiveness of control strategy are verified by experiment results.

# ACKNOWLEDGMENT

This work support by the National Basic Research Program of China (973 Program)(2015CB755800).

#### REFERENCES

- J. Pou, J. Zaragoza, S. Ceballos, M. Saeedifard, D. Boroyevich, "A carrier-based PWM strategy with zero-sequence voltage injection for a three-level neutral-point clamped connverter", *IEEE Transactions on Power Electronics*, vol. 27, no. 2, pp. 642-651, 2012.

- [2] S. Almer, S. Mariethoz, M. Morari, "Sampled Data Model Predictive Control of a Voltage Source Inverter for Reduced Harmonic Distortion", *IEEE Transactions on Control System Technology*, vol. 20, no. 8, pp. 198-209, 2012.

- [3] W. Huimin, W. Kunpeng, Z. Yun, X. Changliang, "Neutral Point Potential Balance Strategy for Three-level Inverter Based on Meticulous Partiion Control", *Transaction of China Electrotechnical Society*, vol. 30, no. 19, pp. 144-150, 2015.

- [4] W. Srirattanawichaikul, S. Premrudeepreechacharn, Y. Kumsuwan, "Modified Unipolar Carrier-Based PWM Strategy for Three-level Neutral-Point-Clamped Voltage Source Inverters", *Journal of Electrical & Technology*, vol. 9, no. 2, pp. 489-500, 2014.

- [5] X. Chang-Liang, X. Zhe, Z. Jia-Xin, "A New Direct Power Control Strategy for NPC Three-level Voltage Source Rectifiers Using A Novel Vector Influence Table Method", *Journal* of Power Electronics vol. 15, no. 1, pp. 106-115, 2015.

- [6] S. Ceballos, J. Pou, E. Robles, I. Gabiola, J. Zaragoza, J. L. Villate, D. Boroyevich, "Three-Level Connverter Topologies With Switch Breakdown Fault-Tolerance Capability", *IEEE Transactions on Industrial Electronics*, vol. 55, no. 3, pp. 982-995, 2008.

- [7] M. Lin, Y.-H. Li, L. Qu, C. Wu, G.-Q. Yuan, "Fault Detection of a Proposed Three-Level Inverter Based on a Weighted Kernel Principal Component Analysis" *Journal of Power Electronics*, vol. 16, no. 1, pp. 182-189, 2016.

- [8] L. June-Seok, L. Kyobeum, "Tolerance Control for the Inner Open-Switch Faults of a T-Type Three-level Rectifier", *Journal of Electronics*, vol. 14, no. 6, pp. 1157-1165, 2014.

- [9] A. Quntao, Diagnosis and Fault-tolerant Control Strategies of Inverters in Three-phase Motor Drive Systems, Hei Longjiang Harbin: Harbin Institute of Technology, 2011.

- [10] L. Ning, L. Ying-hui, Z. Xi-hua, "The FCS-MPC Research for a New Inverter", *International Journal of Electronics*, vol. 38, no. 2, pp. 2375-2380, 2014.

- [11] P. Cortes, M. P. Kazmierkowski, R. M. Kennel, "Predictive control in power electronics and drives" *IEEE Transactions* on *Industrial Electronics*, vol. 55, no. 12, pp. 4312-4324, 2008.

|          | Table 5. Retivation sequence of the fourth leg |              |                  |                |                  |                |                  |                |  |  |  |

|----------|------------------------------------------------|--------------|------------------|----------------|------------------|----------------|------------------|----------------|--|--|--|

| Sequence | Transition between the states                  | $i_{NP} > 0$ | Step1            | Step 2         | Step 3           | Step 4         | Step 5           | Step 6         |  |  |  |

| 1        | $A \rightarrow B$                              | 1            | Deactivate $S_4$ | Activate $S_5$ | Deactivate $S_2$ | Activate $S_1$ | Deactivate $S_5$ | Activate $S_3$ |  |  |  |

| 2        | $A \rightarrow B$                              | 0            | Deactivate $S_2$ | Activate $S_6$ | Deactivate $S_4$ | Activate $S_3$ | Deactivate $S_6$ | Activate $S_3$ |  |  |  |

| 3        | $B \to A$                                      | 1            | Deactivate $S_3$ | Activate $S_5$ | Deactivate $S_1$ | Activate $S_2$ | Deactivate $S_5$ | Activate $S_4$ |  |  |  |

| 4        | $B \to A$                                      | 0            | Deactivate $S_1$ | Activate $S_6$ | Deactivate $S_3$ | Activate $S_4$ | Deactivate $S_6$ | Activate $S_2$ |  |  |  |

Table 3. Activation sequence of the fourth leg

- [12] Y.Hammi, N.Zanzouri, M.Ksouri, "Modeling and Predictive Control of Hybrid System", *International Journal of Computer Science & Emerging Technologies*, vol. 6, no. 2, pp. 333-342, 2011.

- [13] A. Timbus, M. Liserre, R. Teodorescu, P. Rodriguez, F. Blaabjerg, "Evaluation of Current Controllers for Distributed Power Generation Systems", *IEEE Transactions on Power Electronics*, vol. 24, no. 3, pp. 654-664, 2009.

- [14] H. Ma, X.-Y. Mao, D.-H. Xu, "Parameter Identification of DC/DC Power Electronic Circuits Based on Hybrid System Model", *Proceedings of the CSEE*, vol. 25, no. 10, pp. 50-54, 2005. (in Chinese)

- [15] J. Li, S. Englebretson, A. Q. Huang, "Reliability Comparison for 3L-NPC and 3L-ANPC Converters for Drives Application" *IEEE International Electric Machines & Drives Conference (IEMDC)*, pp. 271-276, 2011.

- [16] D. Mignone, Control and Estimation of Hybrid Systems with Mathematical Optimization, Zurich: The Swiss Federal Institute of Technology, 2002.

- [17] Z. Yue, *Modeling and control of hybrid system*, He Bei Bao Ding: North China Electric Power University, 2008.

- [18] Y. Hammi, N. Zanzouri, M. Ksouri, "Fault-Tolerant Model Predictive Control of Hybrid Systems", *International Journal of Computer Applications*, vol. 43, no. 10, pp. 29-36, 2012.

- [19] H. Zhang, S. Finney, A. Massoud, B. W. Williams, "An SVM Algorithm to Balance the Capacitor Voltages of the Three-Level NPC Active Power Filter", *IEEE Transactions* on Power Electronics, vol. 23, no. 6, pp. 2694-2702, 2008.

- [20] X.-T. Sun, L. Un, F.-J. Wu, K. Zhao, "Topology and Control of Single Power Source Hybrid Asymmetrical Multilevel Connverter" *Proceedings of the CSEE*, vol. 29, no. 33, pp. 8-14, 2009.

- [21] J. D. Barros, J. F. A. Silva, E. G. A. Jesus, "Fast-Predictive Optimal Control of NPC Multilevel Converters", *IEEE Transactions on Industrial Electronics* vol. 60, no. 2, pp. 619-627, 2013.

- [22] P. Cortes, J. Rodriguez, C. Silva, "Delay Compensation in Model Predictive Current Control of a Three-Phase Inverter", *IEEE Transactions on Industrial Electronics*, vol. 59, np. 2, pp. 1323-1325, 2012.

- [23] V. Yaramasua, M. Riverab, M. Narimania, B. Wua, J. Rodriguez, "High performance operation for a four-leg NPC

inverter with two-sample-ahead predictive control strategy" *Electric Power Systems Research*, vol. 123, pp. 31–39, 2015.

**Mao Lin** was born in Shaanxi Province, China, in 1988. In 2010 and 2013, he received his B.S. and M.S. degrees in Electrical Engineering from the Air Force Engineering University, Xi'an, China, where he is currently working toward his Ph.D. degree, with focus on fault diagnosis for power electronics systems. His current research interests include power electronics, GPC control, and fault diagnosis of inverters.

Ying-hui Li was born in Guangxi, China, in 1966. She received her B.S., M.S., and Ph.D. degrees in Electrical Engineering from Xi'an Jiaotong University, Xi'an, China, in 1987, 1990, and 2000, respectively. Since 1990, she has been a professor at the School of Aeronautics and Astronautics Engineering, Air Force Engineering University, Xi'an, China. Her research interests include nonlinear control theory on electronics systems, circuits, and control of high-efficiency integrated electric energy conversion in various in-

dustrial fields.

**Ning Li** was born in Shaanxi Province, China, in 1987. He received his B.S. and M.S. degrees in Electrical Engineering from the Air Force Engineering University, Xi'an, China, in 2010 and 2013, respectively. He is currently working toward his Ph.D. degree at the Air Force Engineering University. His research interests include nonlinear control theory and flight safety.

**Chen Wu** was born in Shaanxi Province, China, in 1990. He received his B.S. and M.S. degrees in Electrical Engineering from the Air Force Engineering University, Xi'an, China, in 2011 and 2014, respectively. He is currently working toward his Ph.D. at the Air Force Engineering University, where he is engaged in power electronic modeling. His current research interests include PFC circuit modeling and control research of circuits.

**Jian-Bin Gao** was born in Anhui Province, China, in 1991. He received his B.S. and M.S. degrees in Electrical Engineering from the Air Force Engineering University, Xi'an, China, in 2012 and 2015, respectively. He is currently working toward his Ph.D. degree at the Air Force Engineering University, where he is engaged in fault diagnosis for power electronics systems. His current research interest is fault diagnosis of inverters. AUTHORS' ADDRESSES Mao Lin, M.Sc. Prof. Ying-hui Li, Ph.D. Ning Li, M.Sc. Chen Wu, M.Sc. Jian-Bin Gao , M.Sc. Department of Electrical & Electronics Engineering, Air Force Engineering University, Xi'an, CN-710038, Shaanxi, China email: 496180444@qq.com, liyinghui@126.com, 15129806140@163.com, 262432206@qq.com, doris123@126.com

> Received: 2015-04-25 Accepted: 2016-10-06