# Simulation and Control Strategy of a 5.6 kV 17-level STATCOM Under SVG Condition

DOI 10.7305/automatika.2017.12.1725 UDK 681.537.017:[621.31.051.025.016.4:621.314.54]

Original scientific paper

To achieve high-voltage reactive power compensation, a 5.6kV 17-level STATCOM under SVG Condition is presented. In this paper, we use a cascaded H-bridge multilevel star-connection converter whose system structure and circuit schematic are described. Then by using the phase-shifted carrier modulation strategy and the active-reactive current decoupling method, the STATCOM performs quite well. Moreover modulation strategy of the 17-level STATCOM based on the active disturbance rejection control (ADRC) is presented and the analytical formulas are described. For implementation, control strategy for DC bus voltage balance in cascaded H-bridge multilevel converters, time average distribution method and extreme value offset method are applied in our design. Finally, simulation results demonstrate that the proposed 17-level STATCOM is capable of reactive power compensation, simultaneous controlling and balancing the DC side voltages during the work and verify that high-voltage reactive power can be accurately and effectively compensated.

**Key words:** STATCOM, Static var generation (SVG), Control strategy, Active-reactive current decoupling, Cascaded H-bridge (CHB) multilevel converters, Time average distribution, Extreme value offset

Simuliranje i upravljačka strategija 5.6 kV 17-razniskog STATCOM sustava uz SVG uvjet. Za postizanje kompenzacije jalove snage uz visoki napon, predstavljen je STATCOM s 5.6 kV i 17-razina uz SVG uvjet. U ovom radu koristimo kaskadni višerazinski H-mosni pretvarač u zvijezda spoju uz opisane strukturu i shemu spoja. Zatim korištenjem strategije modulacije s fazno-pomaknutim signalom nosioca i metode rasprezanja radno-jalove struje, STATCOM pokazuje prilično dobro vladanje. Uz to, prikazana je strategija modulacije 17-razinskog STATCOM-a zasnovana na upravljanju s aktivnim odbacivanjem smetnji (ADRC) te su opisane analitičke formule. Za implementaciju, u naš dizajn primjenjene su upravljačka strategija balansiranja napona DC sabirnice u kaskadnom višerazinskom H-mosnom pretvaraču te metoda vremenskog uprosječavanja razdiobe i metoda ekstremne vrijednosti pomaka. Konačno, simulacijski rezultati pokazuju da je predloženi 17-razinski STATCOM sposoban za kompenzaciju jalove snage, istovremeno upravljanje i balansiranje napona DC strane u radu te potvrđuju da je jalovu snagu uz visoki napon moguće točno i djelotvorno kompenzirati.

**Ključne riječi:** STATCOM, proizvodnja energije uz statičku jalovu snagu (SVG), upravljačka strategija, rasprezanje radne-jalove struje, višerazinski H-mosni pretvarači (CHB), vremenski uprosječena razdioba, ekstremna vrijednost odmaka

## 1 INTRODUCTION

In recent years, the major power has been consumed through instantaneous reactive loads like asynchronous motor, synchronous motor, pumps etc. According to the concepts and principles of instantaneous reactive power compensation, the static synchronous compensator (STAT-COM) performs well in the stability of the system voltage, system steady-state and dynamic [1, 2]. Compared with the traditional static var compensator (SVC), it has advantages such as high adjustment speed, wide operation range,

Corresponding author: Fengyu Zhou

continuous compensation, small harmonic current and low loss etc [3]. In addition, two-level inverters which can reduce the harmonics while increasing the capacity are introduced into STATCOM [4]. However the necessary expensive transformer leads to the high system cost and energy consumption. Cascaded H-bridge (CHB) multilevel inverters without transformer are applied in the area of high-voltage and high-power STATCOM [5,6], and those inverters uses multi-level square wave synthesis staircase to obtain sinusoidal output voltage. With the increasing in output voltage level, a better harmonic spectrum is achieved, and switches have low voltage stress. Due to its low cost,

high reliability, security, and good controllability, the CHB STATCOM has been widely applied in the reactive power compensation, power quality control and other fields.

There are many control methods for CHB multilevel STATCOM such as modulation technique based on ladder wave, PWM (pulse width modulation) modulation technique based on space vector (SVPWM), and PWM modulation method based on carrier [7, 8]. All these control methods have their advantages and disadvantages. We can select and use the appropriate control methods in practical applications. CPS-SPWM (carrier phase shifted sinusoidal pulse with modulation) can control output of inverter according to SPWM law in high power applications, improve the output waveform greatly, reduce the output harmonics and reduce cost with smaller filter. On account of its high equivalent switching frequency and wide transmission bandwidth, a variety of advanced control strategies can be used to optimize the overall system performance.

CHB multilevel inverter is connected with DC side capacitors which are isolated from each other, based on this, it exists multi-independent DC bus voltage and unbalanced DC capacitor voltage. Moreover because each H-bridge inverter is a linear, multi-variable and strong coupling system, thus the parallel loss, switching loss, modulation ratio and pulse delay are different among inverters [9, 10]. DC bus voltage balance control is directly related to AC side of inverter output waveform quality, active and reactive power output, voltage and current of switching device, and dynamic response of converter. Unbalanced DC capacitor voltage can decrease the performance of CHB multilevel converter [11].

Given above all, novel control strategies for DC bus voltage balance, time average distribution method and extreme value offset method are applied in this paper. The paper is organized in the following manner. In Section 2, the system structure of STATCOM including the schematic of CHB multilevel converter is reviewed Section 3 describes the modulation strategy of 17-level STATCOM using active-reactive current decoupling. he novel control strategy for DC bus voltage balance in CHB multilevel converters is presented in Section 4 and in Section 5 the simulation results are illustrated. Section 6 is devoted to total voltage of CHB multilevel converters conclusions.

#### 2 SYSTEM STRUCTURE OF STATCOM

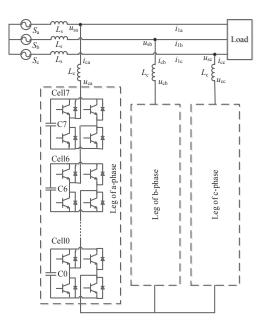

Fig. 1 shows the system structure of STATCOM. In this figure,  $u_{sa}$ ,  $u_{sb}$  and  $u_{sc}$  are grid voltage,  $i_{la}$ ,  $i_{lb}$  and  $i_{lc}$  stand for load current,  $u_{ca}$ ,  $u_{cb}$  and  $u_{cc}$  are voltage of STATCOM,  $i_{ca}$ ,  $i_{c}$  and  $i_{ca}$  are the output current of STATCOM.  $L_c$  is the filter inductance while  $L_s$  is the line inductance. The main circuit of STATCOM is 17-level CHB multilevel converters which is shown in Fig. 1. It consists

Fig. 1. System structure of 17-level STATCOM

of three legs in star-connection and each leg consists of eight cells (H-bridge converter) and filter inductances. The output voltage level be increased by connecting H-bridge converter in sequence. Besides the DC side capacitor of H-bridge converter is independent. STATCOM is mainly used to realize the current reactive power compensation. Energy exchange between the grid and STATCOM is realized by adjusting the phase and amplitude of the STATCOM output voltage, respectively. The amount of exchanged energy is determined by STATCOM active power and load reactive power. 17-level CHB as STATCOM produce high-quality sine wave without transformer. Three small smoothing reactors are required to filter out high-frequency current harmonics generated by STATCOM.

# 3 MODULATION STRATEGY OF 17-LEVEL STATCOM BASED ON ADRC

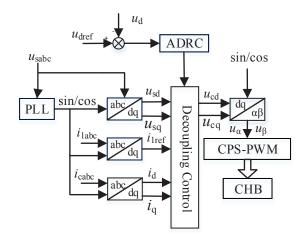

In Fig. 2, the controller detects the reactive component,  $i_{qref}$ , of the load side current,  $i_{labc}$ , by using the park transform and phase-locked loop (PLL). The active and reactive component of  $i_{ab}$ ,  $i_d$ , and  $i_q$  are got from the output current,  $i_{cabc}$ , of STATCOM by Park transform. The active component,  $i_{dref}$ , from PI controller is determined by the DC side reference value,  $u_{dcref}$ , and feedback voltage,  $u_{dc}$ . By Park transform,  $u_{sd}$  and  $u_{sq}$  are got from System voltage,  $u_{abc}$ . All the variables above are used by reactive decoupling controller, and the output voltage vector,  $u_d$  and  $u_q$ , are obtained.Input signal of CPS-PWM, $u_\alpha$ ) and  $u_\beta$ , are got from  $u_d$  and  $u_q$  by dq- $\alpha\beta$  transform. Finally, CSP-PWM generator engender PWM signal. The driving

Fig. 2. Control principle of STATCOM

circuit makes the CHB work, and STATCOM generates the desired reactive power.

### 3.1 CHB switching modulation signals

Among the different pulse generation methods, the PWM which is achieved by comparing reference signal with a high-frequency 'carrier' signal is the most preferred approach in multilevel converters. It has the advantage of switching frequency been fixed and implementation simplicity. Carrier phase-shift PWM (CPS-PWM) is the most commonly used modulation method for H-bridge multilevel converter, because of it's power distribution among all of the CHBs and easy to implement [12–14]. The phase of each carrier signal is shifted in a proper angle to reduce the harmonic of current flowing from each leg and to lower the output current ripple of the CHB.

The modulation method, unipolar dual frequency CPS-SPWM, is used. The working principle is that all H-bridge converters have the same modulation reference signal, and the phase of its triangular carrier signal shifts 1/N of the carrier cycle, and the cascaded H bridge inverters consists of N cells in sequence connection. The carrier phase is shifted half carrier cycle for the two legs of an H-bridge converter, and the same modulation reference sine signal is used to generate the unipolar dual frequency CPS-SPWM. Because a common modulation reference signal is used, the fundamental output is exactly the same. The output of each H-bridge converter can be added together, the general output is N times of single H-bridge output, and the output voltage is 2N+1 level. For the carrier phase shift, the loworder harmonics cancel each other out which leads to the improvements of the equivalent switching frequency.

## 3.2 System control based on ADRC

ADRC is a new type of controller which can inherit the advantage as independent of the object model and im-

prove inherent defects of the traditional PID. ADRC can automatically detect the real-time effects of the system and compensates the error. ADRC detects and compensates the total disturbances of the system, whether internal disturbances or external disturbances. ADRC does well, whether parameters change or uncertain disturbance, which shows that it has strong adaptability, robustness and maneuverability [15].

For the nonlinear uncertain objects of SISO, equation (1) is given as below:

$$y(n) = f(y, \dot{y}, \dots, y^{(n-1)}, t) + \bar{\omega}(t) + bu,$$

(1)

where  $f(y, \dot{y}, \cdots, y^{(n-1)}, t)$  is unknown function,  $\bar{\omega}(t)$  is unknown disturbances, y is measurement output, u is control input.

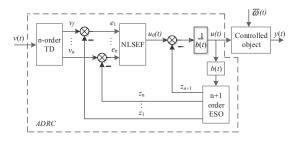

Fig. 3. The diagram of ADRC

The diagram of ADRC corresponding to equation (1) is shown in Fig. 3. It is composed of a tracking differentiator (TD), an extended state observer (ESO), and a nonlinear state error feedback controller (NLSEF). TD realizes the fast non-overshoot tracking of the input signal and gives the reference input of corresponding derivative. ESO can be used to estimate system state, real-time effect of model and external disturbance and compensate it. The nonlinear uncertainty object with unknown interference is controlled as integral tandem object. NLSEF realizes the disturbances compensation control by using the error between the output of the TD and ESO.

The realization of the first order ADRC is given as

$$\begin{cases}

v_{1} = -r \cdot fal\left(v_{1} - v(t), a_{0}, \delta_{0}\right) \\

\varepsilon = z_{1} - y \\

\dot{z}_{1} = z_{2} - \beta_{1} \cdot fal(\varepsilon, a_{1}, \delta_{1}) + bu \\

\dot{z}_{2} = -\beta_{2} \cdot fal(\varepsilon, a_{1}, \delta_{1}) , \\

\varepsilon_{1} = v_{1} - z_{1} \\

u_{0} = \beta_{3} \cdot fal(\varepsilon_{1}, a_{2}, \delta_{2}) \\

u = (u_{0} - z_{2})/b

\end{cases}$$

(2)

$$\text{where } fal(\varepsilon,a,\delta) = \left\{ \begin{array}{ll} |\varepsilon|^a \mathrm{sgn}(\varepsilon) & |\varepsilon| > \delta \\ \varepsilon/\delta^{1-a} & |\varepsilon| \leq \delta \end{array} \right..$$

It can be seen from equation (2) that the input and output of the object, u and y, is needed, which means it is simple and easy to implement.

From Fig. 1, according to the voltage balance of system, mathematical model of the main circuit is obtained in equation (1).

$$L\frac{di}{dt} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} = \begin{bmatrix} u_{sa} \\ u_{sb} \\ u_{sc} \end{bmatrix} - \begin{bmatrix} u_{ca} \\ u_{cb} \\ u_{cc} \end{bmatrix} + R \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix}, \quad (3)$$

where R is a known resistance.

Based on Park transform, equation (3) transforms from abc coordinate to dq coordinate and the sum of three-phase currents is zero in three-phase three-wire system. Mathematical model under dq coordinate is defined in equation (4).

$$L\frac{di}{dt} \begin{bmatrix} i_d \\ i_q \end{bmatrix} = \begin{bmatrix} -R & \omega L \\ \omega L & -R \end{bmatrix} \begin{bmatrix} i_d \\ i_q \end{bmatrix} + \begin{bmatrix} u_{sd} - u_{cd} \\ u_{sq} - u_{cq} \end{bmatrix}, \quad (4)$$

where L is known electrical inductance,  $\omega$  is a known parameter.

Laplace transform is applied to (4) and we can get:

$$Ls \begin{bmatrix} I_d(s) \\ I_q(s) \end{bmatrix} = \begin{bmatrix} -R & \omega L \\ \omega L & -R \end{bmatrix} \begin{bmatrix} I_d(s) \\ I_q(s) \end{bmatrix} + \begin{bmatrix} U_{sd}(s) \\ U_{sq}(s) \end{bmatrix} - \begin{bmatrix} U_{cd}(s) \\ U_{cq}(s) \end{bmatrix}.$$

(5)

Active current  $i_d$  and reactive current  $i_q$  coupled to each other by connection inductance which makes it difficult to control. To obtain the optimal control effect, it is necessary to decouple  $i_d$  and  $i_q$ .

From equation (4), equation (6) can be obtained:

$$\begin{cases} L\frac{dI_d}{dt} = -RI_d + \bar{\omega}_d - U_{cd} \\ L\frac{dI_q}{dt} = -RI_d + \bar{\omega}_q - U_{cq} \end{cases}$$

(6)

Voltage  $u_{sd}$  and  $u_{sq}$  are difficult to measure and uncertainty.  $\bar{\omega}_d = \omega L \cdot I_q + U_{sd}$  and  $\bar{\omega}_q = -\omega L \cdot I_d + U_{sq}$  are internal disturbances.

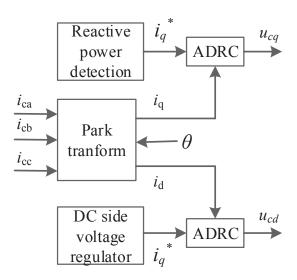

Decoupled d, q axis ADRC is obtained. Diagram of active-reactive decoupling control is shown in Fig. 4.

Reactive power control is described as an example. Reactive current reference from reaction power detection,  $i_q^*$ , is reference of ADRC. Reactive current flowing through STATCOM is output. The output voltage,  $u_{cq}$ , is the control signal. The reactive current follows the change of reference current.

Fig. 4. Diagram of active-reactive decoupling control

According to equation (4), control system of reactive power is 1<sup>st</sup> order and 1<sup>st</sup> order TD is needed. Supposing the output of 1<sup>st</sup> TD is

$$v_1 = -k_1 \cdot fal\left[ (v_1 - i_a^*), a_1, \delta_1 \right], \tag{7}$$

2<sup>nd</sup> order ESO is built and given as below

$$\begin{cases} \dot{z}_1 = z_1 - k_{21} \cdot fal(\varepsilon_2, a_2, \delta_2) - U_{cq} \\ \dot{z}_2 = -k_{22} \cdot fal(\varepsilon_2, a_2, \delta_2) \end{cases}, \tag{8}$$

where  $\varepsilon_2=z_1-i_q$ . NLSEF can be obtained from nonlinear function of system state error feedback,  $\varepsilon=z_1-v_1$ , and is given

$$\begin{cases} u_0 = k \cdot fal(\varepsilon, a, \delta) \\ u_{cq} = (u_0 - z_2) \cdot (-1) \end{cases}, \tag{9}$$

where  $k_1$ ,  $a_1$ ,  $\delta_1$ ,  $k_{21}$ ,  $k_{22}$ ,  $a_2$ ,  $\delta_2$ , k, a, and  $\delta$  are pending parameters.

# 4 CONTROL STRATEGY FOR DC BUS VOLTAGE BALANCE IN CHB MULTILEVEL CONVERT-ERS

There are mainly two kinds of implementations for DC side voltage control strategies used: hardware implementation [2–4, 16] and software implementation [6, 7, 17].

The working principle of hardware implementation is to use hardware circuit to supply DC energy consumption, such as the shunt resistance, AC bus energy exchange and the DC link energy exchange. The aforementioned hardwares are PWM rectifier, diode bridge rectifier and inverter. The differences between these circuits are topology,

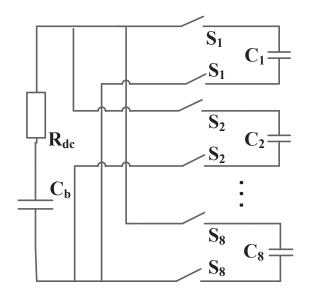

Fig. 5. Working principle of DC bus balance in CHB multilevel converters

energy sources and energy path. The voltage balance effect of hardware implementation method is perfect, however, it is not easy to use due to its high cost, large volume and, low efficiency [17].

By adjusting the pulse width or the phase angle of each cell, software implementation can keep the balance of DC side capacitance voltage, and it is useful for CPS-PWM. Pulse width and phase angle change can make the output voltage of CHB asymmetric, and introduce more harmonics. When the number of cells is higher, it is even worse, and lower frequency harmonics is introduced.

Given above all, a balance control method based on ADRC is applied which can be used in both two cells CHB multilevel inverters and eight cells CHB multilevel inverters in Fig. 5.

The working principle of DC bus balance in CHB multilevel converters is shown in Fig. 5, where  $C_b$  and  $R_{dc}$  are auxiliary capacitance and current limiting resistor respectively. Then simulation is carried out by MATLAB, and balanced DC capacitor voltage can be obtained. In a working period, DC side capacitance exchange energy with the auxiliary capacitance,  $C_b$  and later another DC side capacitance exchange energy with the auxiliary capacitance,  $C_b$ . In a word, extra energy of the DC side capacitance can be send transferred to the auxiliary capacitance, and these the energy will be used by another DC side capacitance. Finally, voltage balance will be achieved.

#### 4.1 Time average distribution method

The method is that each unit is assigned the same time to consume the capacitor energy storage. Based on that, the voltage is achieved balancing. In this paper, DC side capacitance sorted in accordance with the sequence of cell, and the time connecting cell and auxiliary capacitance is the same, thus the charging and discharging probability of each module is the same. As long as the parameters are properly designed, the voltage balance between the modules can be achieved.

#### 4.2 Extreme value offset method

Extreme value offset method is applied to detect unit capacitor and voltage in real time, which passing the stored energy in the capacitor from highest voltage to the lowest one. In this paper, by detecting the maximum and minimum DC side capacitance voltage, and finding the corresponding cell, the energy in the corresponding capacitance will be exchanged. The maximum voltage capacitance transfer energy to the auxiliary capacitance first, then auxiliary capacitance transfer energy to the minimum voltage capacitance. At last, voltage balance between each module can be achieved.

#### **5 SIMULATION RESULTS**

The main goal of the experimental setup is to validate the structure of 17-level STATCOM and its corresponding control strategy. Simulation is carried out to demonstrate the high-voltage reactive power can be accurately and effectively compensated by the proposed methods. The system is established based on MATLAB/Simulink, parameters are described as below: each leg of CHB consists of eight cells in serial connection, DC power supply voltage  $U_d=5.6~{\rm kV}$ , DC side capacitance is  $600~\mu{\rm F}$ , rating voltage is  $700~{\rm V}$ , filter inductance  $L=8~{\rm mH}$ . Suppose that the main circuit switch is ideal switch, carrier frequency is  $10~{\rm kHz}$ , and CHB is in star-connection.

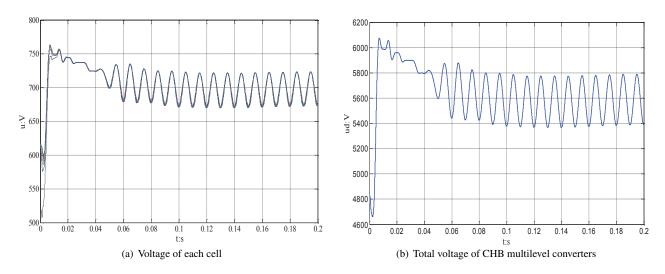

Firstly, in order to show the performance of the control strategy for DC bus voltage balance, the DC side capacitance voltage is tested by using time average distribution method, which is shown in Fig. 6. The DC side capacitance voltage of each cell can be observed in Fig. 6(a), it obviously that the DC bus voltage waveforms of each cell is similar in shape and amplitude. The total voltage of CHB multilevel converter can be observed in Fig. 6(b) where it can be seen that the total voltage is at 5600 V, and volatility is largely controlled within about  $\pm 3.57\%$  after 0.06 s. The voltage shown in Fig. 6 verifies the effectiveness of time average distribution method.

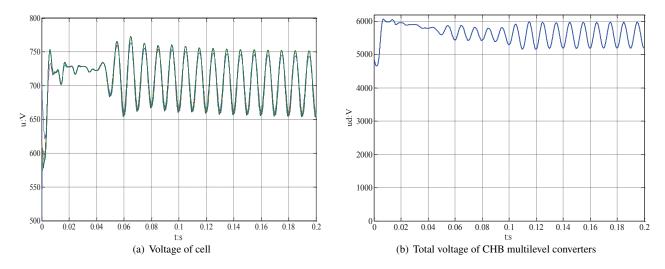

Secondly, a test of the control strategy for DC bus voltage balance is processed; the DC side capacitance voltage using extreme value offset method has been performed. Fig. 7 illustrates the voltage of each cell and the total voltage of CHB multilevel converters. In Fig. 7(a), it is possible to see that the voltage of each cell is stable at 700 V which

Fig. 6. DC side capacitance voltage using time average distribution method

Fig. 7. DC side capacitance voltage using extreme value offset method

Fig. 8. Compensation effect of STATCOM at t=0.2s

is largely controlled within about  $\pm 7.14\%$ , and different from each other. The total voltage varies between 5200 V and 6000 V after 0.02 s, which can be clearly observed in Fig. 7(b).

All these show that the sum of the DC side voltage is robust. Waveforms of capacitance voltage on cell coincide with each other and a balanced capacitance voltage are got. According to the results of figs, the DC side capacitance voltage using time average distribution method is better than using extreme value offset method. The relative voltage ripple of time average distribution method is much smaller than DC voltage control strategy used in [18, 19].

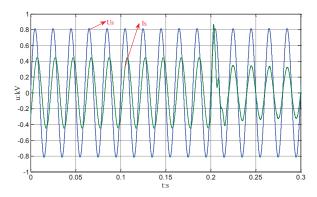

Thirdly, a test on compensation effect of STATCOM with putting into it at  $t=0.2\,\mathrm{s}$ . Although it is not a normal operation of STATCOM. Fig. 8 shows the compensa-

Fig. 9. Compensation results when load changes and the change of reactive current at t=0.4s

tion effect of STATCOM when the STATCOM is accessed. Where  $u_s$  is grid voltage and  $I_s$  is grid load current, respectively. It presents that the phase angle of grid voltage and load current are consistent in substantial, which shows that the power factor of the load side improves significantly, and the output waveform performs in high quality.

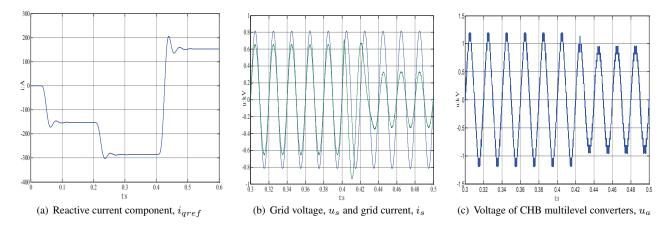

At t = 0.4 s, the load switches from L to C, by this way, it can be tested that the reactive compensation ability of CHB multilevel converters when the load changes from inductive to capacitive. Dynamic simulation waveforms are shown in Fig. 9. The waveform of the reactive current component,  $i_{qref}$  is shown in Fig. 9(a). Fig. 9(b) shows the waveform of grid voltage,  $u_s$  and grid current,  $i_s$ . The waveform of voltage of CHB multilevel converters,  $u_{ca}$  is shown in Fig. 9(c). It illustrates that even in the present of the load change, the system current and the CHB multilevel converters output changes. When system tuning is completed, the CHB multilevel converters output is consistent with the reactive current component both in the amplitude and the phase. Dynamic compensation effect of CHB inverter is better and the correctness of calculation of reference signals is demonstrated yet.

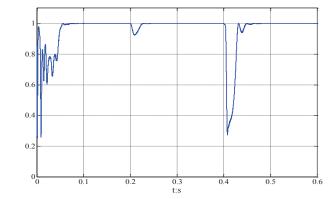

The diagram of power factor is shown in Fig. 10. At  $t=0.2\,\mathrm{s}$ , inductive load is larger. At  $t=0.4\,\mathrm{s}$ , inductive load is zero and capacitive load exists. from the Simulation result, it illustrate that the reactive power compensation effect is obvious and rapid.

# 6 CONCLUSION

A 17-level high-power STATCOM based on ADRC is presented in this paper. The proposed framework includes the schematic of CHB multilevel converter, the operation principle is given and discussed. CSP-PWM is applied in STATCOM and the control signal of 17-level CHB multilevel inverter is obtained by using the active-reactive current decoupling control. Secondly, an appropriate reactive

Fig. 10. Diagram of power factor

current decoupling controller is presented, which compensates in real time and generates ac currents of the CHB based STATCOM that tracks their references with small ripples. Thirdly, the method of energy balance inside the converter is discussed and it shows that the CHB can regulate DC capacitor voltages at a predetermined level well. Finally, simulation results show that the switch can work with low switching frequency.

The proposed controller can perform well in lower switching power losses and higher energy efficiency, as well as heat dissipation reduction and smaller dimensions of the converter. Simulation results verify that the proposed method is verified as an efficient way of reactive power compensation, and simultaneous controlling and balancing the DC side voltages during the working states.

## ACKNOWLEDGMENT

The authors would like to thank the anonymous reviewers for all their constructive comments and insightful suggestions which greatly improve the presentation of this

paper. Project supported by the National Nature Science Foundation of China (No. 61375084) and the Key Program of Shandong Provincial Natural Science Foundation, China (No. ZR2015QZ08)

#### REFERENCES

- [1] Y. Ota, I. Joao, Y. Shibano, et al. A Phase-Shifted-PWM D-STATCOM Using a Modular Multilevel Cascade Converter (SSBC)—Part I: Modeling, Analysis, and Design of Current Control. *IEEE Transactions on Industry Applications*, vol. 51, no. 1, pp. 279-288, 2009.

- [2] C. Ying, G. Qiang, X. Dianguo. Control and performance of a medium-voltage cascade H-bridge STAT-COM// Power Electronics and Motion Control Conference (IPEMC), 2012 7th International, pp.2995-2999, 2012.

- [3] Y. Hu, J. Ren, J. Wang, et al. Control Strategy of Transformerless Connected Cascade STATCOM under Unbalance and Asymmetrical Condition// Power and Energy Engineering Conference (APPEEC), 2012 Asia-Pacific. IEEE, pp.1-4, 2012.

- [4] M. Zhang, X. Zha, J. Sun, et al. Passivity-based Control of Cascade D-STATCOM. Proceedings of the Csee, 2011, 31(15):33-39.

- [5] F. Filho, H. Maia. Z, T H A. Mateus, et al. Adaptive Selective Harmonic Minimization Based on ANNs for Cascade Multilevel Inverters With Varying DC Sources. *IEEE Transactions on Industrial Electronics*, vol. 60, no. 60, pp.1955-1962, 2013.

- [6] S. -L. Shen, J. -C. Chen. Study on STATCOM Based on New Hybrid Cascade Multilevel Inverter. *Electrical Measurement & Instrumentation*, 2013.

- [7] C. -D. Townsend, T. -J. Summers, R. -E. Betz. Multigoal heuristic model predictive control technique applied to a cascaded H-bridge StatCom. *IEEE Trans*actions on Power Electronics, vol. 27, no. 3, pp.1191-1200, 2012.

- [8] K. Wang, M. -L. Crow. Power system voltage regulation via STATCOM internal nonlinear control. *IEEE transactions on Power systems*, vol. 26, no. 3, pp.1252-1262, 2011.

- [9] Y. Li, B. Wu. A novel DC voltage detection technique in the CHB inverter-based STATCOM. *IEEE Transactions on Power Delivery*,vol. 23, no. 3, pp.1613-1619, 2008.

- [10] S. Agarwal,S. -R. Deore. Level shifted SPWM of a seven level cascaded multilevel inverter for STAT-COM applications// 2015 International Conference on Nascent Technologies in the Engineering Field (IC-NTE).pp.1 - 7, 2015.

- [11] X. Shi, Z. Wang, Tolbert. L. M, et al. A comparison of phase disposition and phase shift PWM strategies for modular multilevel converters// Enrgy Conversion Congress and Exposition (ECCE), 2013 IEEE, pp.4089-4096, 2013.

- [12] Q. Tu, Z. Xu, L. Xu. Reduced Switching-Frequency Modulation and Circulating Current Suppression for Modular Multilevel Conveners, *IEEE Transactions on Power Delivery*, Vol. 26, No. 3, pp. 2006-2017, Mar. 2011.

- [13] U. -N. Gnanarathna, A. -M. Gole, R. -P. Jayasinghe, Efficient Modeling of Modular Multilevel HVDC Converters(MMC) on Electromagnetic Transient Simulation Programs, *IEEE Transactions on Power Deliv*ery, Vol. 26, No. 1, pp. 316-324, Jan. 2011.

- [14] M. Guan, Z. Xu. Modeling and Control of a Modular Multilevel Converter-Based HVDC System Under Unbalanced Grid Conditions. *IEEE Transactions* on *Power Electronics*, Vol. 27, No. 12, pp. 4858-4867, 2012.

- [15] X. L. Xu, Y. P. Zou, J. Guo, Control System of Cascade Multilevel Statcom Based on Auto-disturbance Rejection Controller[J]. Proceedings of the CSEE, Vol. 31, No. 27, PP. 40-44, 2007.

- [16] M. Saeedifard, R. Iravani, Dynamic Performance of a Modular Multilevel Back-to-Back HVDC System, *IEEE Transactions on Power Delivery*, Vol. 25, No. 4, PP. 2903-2912, Oct. 2010.

- [17] S. Debnath, J. Qin, B. Bahrani, et al. Operation, Control, and Applications of the Modular Multilevel Converter: A Review. *IEEE Transactions on Power Electronics*, Vol. 30, No. 1, pp. 37-53, 2015

- [18] Z. Liu, Z. Xu, W. Liu. Novel strategy of capacitor voltage balancing control for cascaded STATCOM based on advanced carrier phase shifting SPWM. *High Voltage Apparatus*, pp.014, Dec. 2012.

- [19] B. Wang, C. Bai, H. Chen, et al. Cascade-STATCOM DC voltage control strategy based on CPS-SVPWM modulation. *High Voltage Apparatus*, pp.029 Dec. 2015.

Hongchang Sun was born in 1977 in Shandong Province, China. He received his M.S. degree in Control Engineering from the school of control science and engineering at Shandong University, Jinan, China. Now he is engaged in the intelligent electric scientific research and design, Jinan, China. His research interests include electrical intelligent.

Fengyu Zhou was born in 1969 in Shandong Province, China. He received his Ph.D. degree in electrical engineering from Tianjin University, Tianjin, China, in 2008. He is currently a Professor of the School of Control Science and Engineering at Shandong University, Jinan, China. His research interests include robotics and automation.

Yugang Wang was born in 1988 in Shandong Province, China. He is currently a Ph.D. candidate in the school of control science and engineering at Shandong University, Jinan, China. He received his B.S. degree in Mathematics and Applied Mathematics from the colleage of sciences at China University of Mining and Technology, Xuzhou, China, in 2014. His research interests include iterative learning control and service robotics.

AUTHORS' ADDRESSES

Sun Hongchang, M.Sc.

Prof. Zhou Fengyu, Ph.D.

Wang Yugang, M.Sc.

Automation Department,

School of Control Science and Engineering,

Shandong University,

Jing Shi Road 17923, CN-250061 Jinan, Shandong,

China

email: sunhongch@163.com, zhoufengyu@sdu.edu.cn,

1104381659@qq.com

Received: 2016-03-12 Accepted: 2017-08-07