# **Automatika**

Journal for Control, Measurement, Electronics, Computing and Communications

ISSN: 0005-1144 (Print) 1848-3380 (Online) Journal homepage: https://www.tandfonline.com/loi/taut20

# Time-efficient fault detection and diagnosis system for analog circuits

Qiwu Luo, Yigang He & Yichuang Sun

**To cite this article:** Qiwu Luo, Yigang He & Yichuang Sun (2018) Time-efficient fault detection and diagnosis system for analog circuits, Automatika, 59:3-4, 302-310, DOI: 10.1080/00051144.2018.1541644

To link to this article: <a href="https://doi.org/10.1080/00051144.2018.1541644">https://doi.org/10.1080/00051144.2018.1541644</a>

| 9            | © 2018 The Author(s). Published by Informa<br>UK Limited, trading as Taylor & Francis<br>Group |

|--------------|------------------------------------------------------------------------------------------------|

|              | Published online: 07 Nov 2018.                                                                 |

|              | Submit your article to this journal 🗗                                                          |

| <u>lılıl</u> | Article views: 186                                                                             |

| a<br>Q       | View related articles 🗗                                                                        |

| CrossMark    | View Crossmark data 🗗                                                                          |

#### **REGULAR PAPER**

# Time-efficient fault detection and diagnosis system for analog circuits

Qiwu Luo <sup>o</sup>a, Yigang He<sup>a</sup> and Yichuang Sun<sup>b</sup>

<sup>a</sup>School of Electrical Engineering and Automation, Hefei University of Technology, Hefei, People's Republic of China; <sup>b</sup>School of Engineering and Technology, University of Hertfordshire, Hatfield, UK

#### **ARSTRACT**

Time-efficient fault analysis and diagnosis of analog circuits are the most important prerequisites to achieve online health monitoring of electronic equipments, which are involving continuing challenges of ultra-large-scale integration, component tolerance, limited test points but multiple faults. This work reports an FPGA (field programmable gate array)-based analog fault diagnostic system by applying two-dimensional information fusion, two-port network analysis and interval math theory. The proposed system has three advantages over traditional ones. First, it possesses high processing speed and smart circuit size as the embedded algorithms execute parallel on FPGA. Second, the hardware structure has a good compatibility with other diagnostic algorithms. Third, the equipped Ethernet interface enhances its flexibility for remote monitoring and controlling. The experimental results obtained from two realistic example circuits indicate that the proposed methodology had yielded competitive performance in both diagnosis accuracy and time-effectiveness, with about 96% accuracy while within 60 ms computational time.

Vremenski učinkoviti sustav za detekciju kvara i dijagnostiku analognih sklopova. Vremenski učinkovita analiza i dijagnostika analognih sklopova najvažniji su preduvjeti za online monitoring elektroničke opreme koji uključuje kontinuirane izazove sveobuhvatne integracije, tolerancije komponenata, ograničene točke provjere uz višestruke kvarove. U radu je predstavljen analogni sustav za dijagnostiku kvarova zasnovan na FPGA i primjeni dvodimenzionalne fuzije informacija, analizi mreže s dvostrukim priključkom i teoriji intervala. Predloženi sustav ima tri prednosti u odnosu na tradicionalne. Prvo, posjeduje visoku brzinu proračuna i povoljnu arhitekturu sklopa gdje se ugradbeni algoritmi izvršavaju paralelno na FPGA. Drugo, struktura sklopovlja kompatibilna je s drugim dijagnostičkim algoritmima. Treće, postojeće Ethernet sučelje dodatno ističe fleksibilnost sustava za daljinski nadzor i upravljanje. Eksperimentalni rezultati prikupljeni u dva realistična primjera sklopovlja pokazuju da je predložena metodologija rezultirala u kompetitivnim svojstvima dijagnostičke točnosti i vremenske učinkovitosti, uz oko 96% točnosti unutar 60 ms potrebnih za proračune.

#### KEYWORDS

Fault diagnosis; field programmable gate array (FPGA); orthogonal technique; information fusion; analog circuits

#### KLJUčNE RIJEČI

Dijagnostika kvara; FPGA; ortogonalna tehnika; fuzija informacija; analogni sklopovi

# 1. Introduction

From fault dictionary [1-3], parameter identification [4,5] and fault verification [6] before 1990s to following neural network [7,8], fuzzy theory [9] and wavelet analysis [10], the past five decades have witnessed an unprecedented development in the field of analogue detection and diagnosis [11], especially in the study of basis theories, which provide theoretical foundations and probabilistic methods for overcoming the conundrums of component tolerance and nonlinearity. However, with the rapid growth of production technology in electronic circuit domain, the traditional fault diagnosis and detection approaches are costly and time-consuming to some extent, thus cannot wholly satisfy the real-time requirements [12,13]. Moreover, the corresponding platform for these applications is often limited [14]. In order to improve the manufacture efficiency, reduce the maintenance cost and enhance the product quality, the research on real-time

and cost-effective fault detection and location system for analog circuits becomes increasingly crucial.

There are certain major difficulties in automatic fault detection and online diagnosis which are presented as follows.

(1) In the analog world, an increasing number of engineers benefit from various Electronic Design Automation (EDA) tools. To be sure, this tool-based simulation methodology helps us to understand the working principles and theoretical characteristics of certain circuits but confined to the small-scale. Hence the large-scale circuit should be divided into many parts, and each analogue sub-circuit is simulated independently, ignoring the correlations between faulty and fault-free ones. Moreover, due to influences of component tolerance, signal crosstalk and ubiquitous electromagnetic interference (EMI) in actual circuit board, the comprehensive fault simulation of complex mixed signal circuits is almost infeasible only relying on current EDA tools.

- (2) The traditional PC-based fault diagnosis system often cannot achieve online detecting and monitoring, because the circuit parameters are continuously sampled at the MHz-level or even GHz-level rate for the large-scale and wide bandwidth diagnostic objects. In such an extremely short period of time, massive data is gathered then transmitted, the real-time computation for uninterrupted health monitoring and fault locating is usually impracticable to PC.

- (3) There are lots of fault features in analog circuits, the scientific feature selection strategy is a crucial issue which is hard to build.

- (4) Most electronic products are continuously working on the project site which can not be uninstalled for testing. The good sign is that some remote approaches like [15] are arising, but there still exists a long way for us to

This research presents a prototype of fault diagnosis system and tries to do some works to overcome the problems described above. The field programmable gate array (FPGA) is by far parallel and highly reconfigurable, permitting rapid prototyping of control mechanisms and new algorithms for pre-research and realworld applications. It has been extensively used in real-time health monitoring of power converter [16], vibration detection and diagnosis [17] and ionizing radiation testing [18] among others due to its parallel data analysis capabilities. Therefore, application of FPGA in analog circuit fault diagnosis and health management field possesses strong vitality, which can not only provide public test-bench for the present fault diagnosis algorithms, also provide the new idea and implementation scheme for fault monitoring and prediction. Unfortunately FPGA, specialized in parallel data processing, is not widely used for analog circuit fault diagnosis and identification in recent literature.

Jurišić et al. proposed a frequency domain approach for single hard fault location, the experimental results carried out from an active fourth-order LP filter proved its effectiveness [19]. Two years later, this diagnosis method was optimized by applying a binary logical manipulation algorithm, this kind of fault dictionary optimization technique was effective to save time in the minimal test frequencies exploring stage [20]. Generalized from these dictionary-based fault analysis approaches in the frequency domain, M. Peng et al. proposed a fault diagnosis method based on circuit gain under different frequencies [21]. Further more in this article, we considered the circuit node voltage, characteristics of amplitude frequency (A-F) and phase frequency (P-F) as the raw circuit features. Then a hardware main-board is built to capture the fault features and compute the fault location. Two application cases aiming at band pass filter and notch filter are also presented, the testing results prove that the FPGAbased scheme and diagnosis approach can provide a

compatible test-bench and feasible blueprint for the implementation of recent fault diagnosis theories.

The remaining part of this paper is organized in the following way. Section 2 focuses on extraction strategy of fault features. The system design overview is provided in Section 3. In Section 4, the wideband and synchronous data acquisition approach and orthogonal theory are stated. Section 5 describes the fault diagnosis algorithm then proposes the location regulation, followed by our experimental measurement and related results based on a notch filter. Section 6, finally, presents the conclusion of this research.

# 2. Requirement analysis about the fault feature extraction

It is the rapid development of automatic control technology and demand of product miniaturization that lead to the promotion of electronics integration and expansion of manufacturing scale. However, this process has inescapable problems such as weld, adhering tin, printed circuit board (PCB) deformation and device parameter fluctuation and so on, all of which become obstacles to the high stability and strong consistency of manufacture. In order to further enhance product integration, simplify PCB design process and shorten the cycle of product development, IC producers like ADI, Silicon LAB and TI supply a great number of monolithic mixed signal processors based on MCU or DSP for specialized analog circuit, then this kind of core can be constructed as a complete system only with a small quantity of passive devices, Undoubtedly, this great development brings out the prosperity of communication and electronic industries, however, the large scale of mixed signal analog circuits make the online fault detection and diagnosis increasingly complex and unwieldy, and how to safeguard the normal operation of electronic devices in real time has become the bottleneck.

In view of the above situation, combined with present circuit diagnosis theories, we aim to build a high performance system for analog fault detection and diagnosis. On the one hand, this system should be equipped with multi-channel high precision signal acquisition and analysis function, which can extract fault features by measuring the accessible node voltage. On the other hand, it should provide arbitrary waveform generator and wide bandwidth acquisition channels, relying on them, we can analyse the input/output characteristics of analog network.

## 3. Architectural structure design

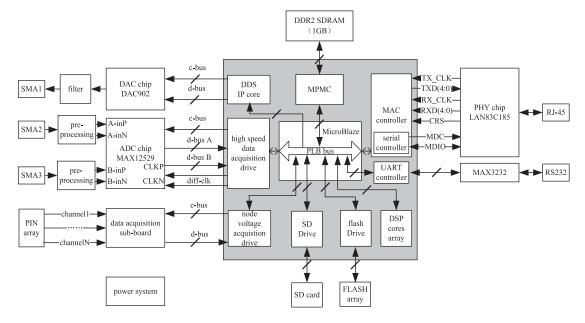

This section puts forward the hardware scheme of the fault detection and diagnosis platform, its structure diagram is shown in Figure 1, the model of the main processor is XC3SD3400A (belongs to Spartan-3A DSP series, Xilinx). The signal generation part is

Figure 1. Topology structure of the proposed analogue fault detection and diagnosis system. It is organized according to the direction of signal flow (which is from left to right), and all the modules in the dotted grey box are implemented in FPGA chip.

consist of the digital to analog converter (DAC902, 165Msps/12-Bit) and the direct digital synthesizer (DDS) module. Then, the frequency sweep signal can be generated from SAM1 port, playing a role of the arbitrary signal source for analog circuit under test (CUT). When it comes to the data acquisition part, there are two different signal objects: for AC signals, we choose MAX12529, which is a dual channel signal acquisition chip owning high-performance up to 96Msps/12-Bit, hence the input/output signals of a certain circuit can be captured by this system through SMA2 and SAM3 respectively. For DC signals, in order to simplify design and enhance the flexibility, we developed it as sub-board form, so node voltage can be gathered through the interface of PIN array. As for the DSP cores being constituted with DSP48E slices, LUTs, dualport block RAMs, and FIFOs, experimenters could rebuild them flexibly for their special design goal. In addition, the system is equipped with sufficient DDR2 SDRAM and Flash memories for computational variables and algorithm operation. Further, the raw gathered information and calculational data can be transmitted to remote host via the flexible Ethernet interface. A 32-bit embedded software processor, MicroBlaze, is used for global management.

# 4. Detection of fault features

It is widely accepted that the technology of fault diagnosis based on node voltage is becoming more and more mature, which has been studied in a large number of literatures [21,22]. So in this section, we do not repeat it again to avoid cumbersome, but demonstrate the real-time data acquisition and online fault location technologies based on the A-F and P-F characteristics.

# 4.1. Approaches of amplitude and phase detection

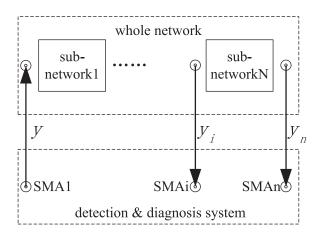

Digital amplitude and phase discrimination is widely used in intermediate frequency (IF) area. Because of the improvement of measurement speed and antiinterference ability, FPGA-based digital intermediate frequency (DIF) system is applied extensively in radar and communication systems [23]. Hence, it is practicable to apply digital methods for analogue fault diagnosis. Generally, large-scale analog circuits, such as multistage operational amplifier and active/passive filter circuits, could be divided as several subnetworks, each two-port subnetwork is connected in head to tail manner. As shown in Figure 2, our detection and diagnosis system generates a controllable signal from interface of SMA 1, acting as a driving source for the whole CUT, then acquires the intermediate signals  $(y_i)$  and final signal  $(y_n)$  via SMAi and SMAn, these information play the role of diagnostic algorithms. Furthermore, a simple MUX test middleware was developed to support the rotational scanning on the various signals of  $y_i$  and  $y_n$ , which benefits to the acquisition channel saving for our diagnosis system.

With Microblaze as the controller of the DDS IP core, the frequency, phase and amplitude of the driving signal are programmable and adjustable. The sampling frequency of ADC (MAX12529) was set to 80 MHz for the necessary safety margin, and two ADC channels were equipped in our diagnosis system. If we suppose the expression of the driving signal is  $y = sin(\omega t)$ , the input and output signal pairs of the subnetwork in Figure 2 can be respectively expressed as  $y_1(t) = A_1 \sin(\omega t + \phi)$  and  $y_2(t) = A_1 A_2 \sin(\omega t + \theta)$ , then are imported to the fault detecting system through SMA2 and SMA3. The embedded DSP algorithms in FPGA can calculate the amplitude and phase according

Figure 2. Testing diagram for analog network.

to (1)–(4) using the orthogonal technique.

$$k_{11} = \sum_{n=0}^{N-1} y_1 \left( \frac{nT}{N} \right) \times \cos \left( \frac{\omega nT}{N} \right)$$

$$= \sum_{n=0}^{N-1} \left( \frac{1}{2} A_1 \sin \left( \frac{2\omega nT}{N} + \phi \right) + \frac{1}{2} A_2 \sin \phi \right)$$

$$= \frac{N}{2} A_1 \sin \phi, \tag{1}$$

$$k_{12} = \sum_{n=0}^{N-1} y_1 \left( \frac{nT}{N} \right) \times \sin \left( \frac{\omega nT}{N} \right)$$

$$= \sum_{n=0}^{N-1} \left( \frac{1}{2} A_1 \cos \phi - \frac{1}{2} A_1 \cos \left( \frac{2\omega nT}{N} + \phi \right) \right)$$

$$= \frac{N}{2} A_1 \cos \phi, \tag{2}$$

$$k_{21} = \sum_{n=0}^{N-1} y_2 \left( \frac{nT}{N} \right) \times \cos \left( \frac{\omega nT}{N} \right)$$

$$= \sum_{n=0}^{N-1} \left( \frac{1}{2} A_1 A_2 \sin \left( \frac{\omega nT}{N} + \theta \right) + \frac{1}{2} A_1 A_2 \sin \theta \right)$$

$$= \frac{N}{2} A_1 A_2 \sin \theta, \tag{3}$$

$$k_{22} = \sum_{n=0}^{N-1} y_2 \left( \frac{nT}{N} \right) \times \sin \left( \frac{\omega nT}{N} \right)$$

$$= \sum_{n=0}^{N-1} \left( \frac{1}{2} A_1 A_2 \cos \theta - \frac{1}{2} A_1 A_2 \cos \left( \frac{2\omega nT}{N} + \theta \right) \right)$$

$$= \frac{N}{2} A_1 A_2 \cos \theta, \tag{4}$$

where T is the excitation signal period, N is the discretized number of one signal period. As for the theoretical derivation above, choosing certain integral number of periods (suppose K periods for an example) for calculating the average value of each intermediate variable is highly recommended for reducing the system error. Finally, the circuit parameters amplitude (5), phase (6) and network gain (7) can be deduced from (1) to (4).

$$\begin{cases} (1)/(2) \Rightarrow \phi = ac \tan(k_{11}/k_{12}) \\ (1)^2 + (2)^2 \Rightarrow A_1 = (2/N)\sqrt{k_{11}^2 + k_{12}^2} \end{cases}, (5)$$

$$\begin{cases} (3)/(4) \Rightarrow \theta = ac \tan(k_{21}/k_{22}) \\ (3)^2 + (4)^2 \Rightarrow A_2 = \left( (2/N)\sqrt{k_{21}^2 + k_{22}^2} \right) / A_1 \end{cases}$$

(6)

$$Network_{gain} = A_2/A_1. (7)$$

These parameters can be migrated to host server and observed clearly on the software interface. Consequently, it is possible for us to monitor the components' status and predict the parameter change trend, which mainly results from random environment variation and limited device lifetime. The proposed online detection approach constitutes a favourable foundation and condition for circuit health monitoring, fault location and prediction.

## 4.2. Two-port network example

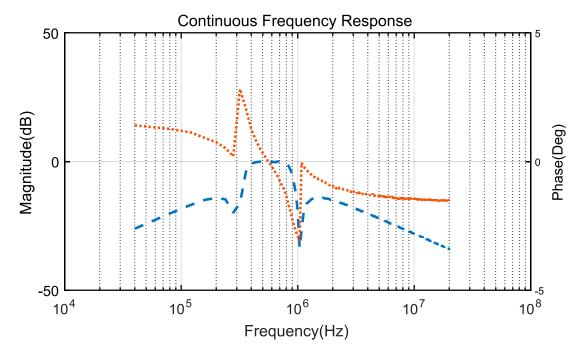

A Chebyshev band pass filter is presented as a typical example, although its amplitude-frequency characteristic is not as flat as that of Butterworth type, it is still widely applied in communication projects because of its fast transition band attenuation speed and minimum error compared with frequency response curve of ideal filter. The third-order Chebyshev type II band pass filter is designed as Figure 3, its design objectives are: Centre Frequency is 562 kHz, Pass Band Width is 500 kHz, Stop Band Width is 650 kHz, Stop Band Ratio is 1.3, Stop Band Attenuation is 13.96 dB. Obviously, as a result of the limitation of the capacitance and inductance parameters in engineering application, we have no choice but to choose the nearby ones, besides, the PCB distribution parameters more or less affect the ultra-small parameters of these passive components. What is more, the higher the frequency of these analog circuits is, the more probably the soft faults occur, which are very confused with component legal parameters. As what is concluded from the above that the real-time fault monitoring becomes seriously complex, the proposed orthogonal approach can avoid the obstacles through analysing the transfer characteristics of sub network. With this raw data, we can identify which subnetworks performance has decreased and then locate its related fault component(/s) fusing with node voltage.

Figure 3. Band-pass filter circuit.

Figure 4. Amplitude–frequency curve and phase–frequency curve.

# 4.3. Detection results analysis

The frequency of the scan signal varies from 0 Hz to 20 MHz, where the frequency scale is logarithmic and its step equals 0.05. The high-speed data acquisition module captures the network signals through SMA2 and SMA3 after the initialization of DDS module, then the customized DSP cores embedded in FPGA complete the orthogonal calculation according to (1)–(7), finally the computing results are submitted to the host software via Ethernet. The accumulation and multiplication executed in FPGA are real-time, while the calculation for square root and arctangent can be performed by CORDIC (Coordinate Rotation Digital Computer) algorithm which needs only 26 operating clock cycles. Suppose FPGA's main operation frequency is 160 MHz configured by digital clock manage (DCM) module, the delay between feature values output and raw signals input is less than 200 ns, which meets the real-time requirements of detection and tracking for amplitude and phase characteristics. Figure 5 shows the continuous frequency response diagram for the band pass filter from the host software, it can be clearly seen that the band pass filter frequency response achieves the design

objectives. Theoretically, most of the hard or soft faults are surely reflected in the frequency response curve [24], if we combined that with the look-up table of node voltage, circuit faults can be quickly analysed and accurately located.

# 5. Fault diagnosis

# 5.1. Theories of fault diagnosis

# A. Parameter selection of the feature interval vector

Hard fault is considered as a special case of soft fault, the original feature vector (FV) of the circuit is set up by various circuit parameters: node voltage, A–F and P–F characteristics.

$$FV = (f n_1, \dots, f n_{N1}, f a_1, \dots, f a_{N2}, f p_1, \dots, f p_{N3}),$$

(8)

where  $f_n$ ,  $f_a$ ,  $f_p$  respectively stand for the node voltages, characteristics of A–F and P–F, and N1, N2, N3 are the corresponding total number of them. To simplify the derivation, here we define N1+N2+N3=N, hence we can rewrite (8) as

$$FV = (f_1, f_2, \dots, f_N),$$

(9)

Figure 5. Notch filter circuit as an example.

where  $f_i(j=1, \ldots, N)$  is the jth circuit parameter of the feature vector. Then we suppose there are *M* circuit modes including fault and normal ones, then the feature interval vectors can be defined as

$$FI_i = ((L_{i1}, R_{i1}), (L_{i2}, R_{i2}), \dots, (L_{iN}, R_{iN})),$$

$$i = 1, \dots, M,$$

(10)

where  $L_{ij}$ ,  $R_{ij}$  (j = 1, ..., N) are the lower bound and upper bound of the *j*th circuit parameter of the *i*th circuit mode, for a certain circuit, they can be calculated from PSpice with Monte-Carlo method and verified by the data acquisition module designed in Section 4.

# B. Circuit similarity of the sample to the feature interval vector

The distinct circuit mode can be reflected by the feature interval vector. Thus the fault diagnosis problem is translated to evaluating the correlation degree between the test sample and the feature interval vectors, which could be represented by the membership degree.

A test sample (TS) is given

$$TS = (ts_1, ts_2, \dots, ts_N), \tag{11}$$

then,  $\epsilon_{ij}$  can be defined as "interval similarity" of the TS to the feature interval  $(L_{i,j},R_{i,j})$  as

$$\varepsilon_{ij} = \begin{cases} 1, (i,j) \in I \\ 1 - \frac{\eta_{ij}}{\sum\limits_{i=1}^{M} \eta_{ij}}, (i,j) \notin I \end{cases} , \qquad (12)$$

where  $I = \{(i, j) \mid L_{ij} \leq TS_j \leq R_{ij}, i = 1, ..., M,$ j = 1, ..., N, and  $\eta_{ij}$ , namely the "interval relative distance" of TS to the feature interval  $(L_{i,j}, R_{i,j})$  is denoted as

$$\eta_{ij} = \frac{\min\{|TS_j - L_{ij}|, |TS_j - R_{ij}|\}}{|L_{ij} - R_{ij}|}, j = 1, \dots, N.$$

The narrower gaps between  $TS_i$  and two boundaries and the larger feature interval, the lower  $\eta_{ij}$  and the larger  $\epsilon_{ij}$  but within 1. Only when  $L_{ij} \leq TS_j \leq R_{ij}$ , the  $\epsilon_{ii}$  equals to 1. Further, the circuit similarity can be derived as

$$\varepsilon_i = \frac{1}{N} \sum_{j=1}^{N} \varepsilon_{ij}, i = 1, \dots, M, \tag{14}$$

which stands for the circuit similarity of the TS to the ith feature interval vector under information fusion of N circuit parameters.

# C. Information fusion-based diagnosis principle

Theoretically, only considering single kind of circuit parameters would trigger fuzzy diagnostic results as a result of the component tolerance [24], so an information fusion techniques involving multiple features are used in our work.

According to the frequency sweeping method, we choose the whole testing bandwidth as 20 MHz (Mega Hertz), the total number P of the selected frequency points equals 146 which calculated from (15), and the frequency logarithm step is 0.05.

$$P = (1/0.05)\log(20 \,\text{MHz}) = 146.$$

(15)

Then a circuit similarity matrix is denoted as

$$\Gamma = \begin{bmatrix} \varepsilon_{11} & \varepsilon_{12} & \cdots & \varepsilon_{1P} \\ \varepsilon_{21} & \varepsilon_{22} & \cdots & \varepsilon_{2P} \\ \vdots & \vdots & \ddots & \vdots \\ \varepsilon_{M1} & \varepsilon_{M2} & \cdots & \varepsilon_{MP} \end{bmatrix}, \quad (16)$$

where  $\epsilon_{ik}$  ( $i = 1, \ldots, M$  and  $k = 1, \ldots, P$ ) is circuit similarity, M and P are the totality of circuit modes and the discrete frequencies. If suppose that the reliability of different input with selected frequency is

$$W = (\omega_1, \dots, \omega_P)^{\mathrm{T}}, \tag{17}$$

then the final similarity of the TS to circuit modes can be rewritten as

$$\varepsilon = \Gamma \times W = [\varepsilon_1, \varepsilon_2, \dots, \varepsilon_M]^{\mathrm{T}},$$

(18)

## Algorithm 1 Identifying the faults of analog circuits.

The current similarity vector  $\varepsilon_{cur}$  to be handled. Output: Fault status (FS), equals "1" if be suffered with fault(s). Main procedure: Initialize the FS = 0, calculating the maximum final similarity  $\varepsilon_{\max 1}$ , the second maximum final similarity  $\varepsilon_{\max 2}$ , the average value of all final similarities  $\varepsilon_{avq}$  from  $\varepsilon_{cur}$ 2.  $\textit{IF} \varepsilon_{\max 1} > \delta \text{ and } \varepsilon_{\max 2} - \varepsilon_{\max 1} > \theta$ 3. 4. **ELSEIF** $\varepsilon_{\text{max 1}}/\varepsilon_{avq} > \lambda$ 5. FS = 16. 7. ELSE FS = 08. **ENDIF** Return FS

where

$$\varepsilon_i = \sum_{k=1}^{P} \varepsilon_{ik} \omega_k, i = 1, \dots, M.$$

(19)

Applying the predefined  $\epsilon_i$  in (14),  $\epsilon_i$  defined in (19) stands for the final similarity of the TS to the ith circuit mode using information fusion of N parameters of circuits obtained from *P* frequency points.

Refer to [24],  $\omega_k$  ( $k=1,\ldots,P$ ) in (17) could be defined as

$$\omega_k = \alpha_k \beta_k / \sum_{k=1}^P \alpha_k \beta_k, \alpha_k = \max_{i=1,...,M} \{\varepsilon_{ik}\}, \beta_k$$

$$= \alpha_k / \sum_{i=1}^M \varepsilon_{ik}.$$

The larger the final similarity, the higher is the probability that the corresponding component is the fault one. And it is widely accepted that the maximum and the second maximum final similarities of  $\epsilon_i$  ( $i = 1, \ldots,$ M) possess higher fault probability. The pseudo codes of fault diagnostic rules is presented in Algorithm 1. The reason of fuzziness would be that some distinct fault modes take the same or similar maximum values of final similarity, while our adopted information fusionbased techniques suppressed these fuzzy decisions to large extent, through considering three basically independent kinds of significant circuit features.

# 5.2. Diagnosis example circuit

The notch filter is popularly used in the fields of radar and sonar, communication, measuring instruments, etc. owing to the selective characteristic for specific frequency band [25-27]. In order to evaluate the realtime efficiency and computing capacity of the realized system, we have diagnosed the notch filter circuit in Figure 6 [27], the component parameters are given in Figure 6 and the parameter precision is 1%, the trap centre frequency is 275.6 Hz. The input node 7 and output node 9, together with intermediate nodes 1, 2, 3, 4 and 8 are selected as accessible nodes, thus, the voltage

Figure 6. The actual circuit of notch filter.

Figure 7. The FPGA-based dignosis platform.

of accessible nodes V7, V9, V1, V2, V3, V4, V8 constitute a kind of test signal. And the A-F and P-F characteristics are captured by the MAX12529 as another two kinds of test signals. Consequently, the value of the circuit parameters N defined in (9) equals 9. The photograph of its actual circuit has given in Figure 7.

# 5.3. Diagnosis results and further analysis

In the literature [28], Peng et al. selected A-F characteristic as a set of feature information for fusion technology by selecting six frequency points from the limited frequency range (0-45 kHz), and combined with the traditional node voltage detection technology, the correct diagnosis rate after fusion was increased by approximately 10% than that using one single information. Furthermore in this paper, we choose the node voltage, A-F and P-F characteristics distributed in the whole bandwidth from 0 to 20 MHz as three kinds of fusion information. Figure 7 gives the designed test platform.

We suppose that there is an independent relationship between each hard fault of the notch filter shown in Figure 5, then all the faults can be divided into two

(i) 16 kinds of hard faults caused by single component open-circuit or short-circuit;

| Fault category | Diagnosis method | Location result |    |    |    |    |    |    |    |    |            |

|----------------|------------------|-----------------|----|----|----|----|----|----|----|----|------------|

|                |                  | N               | R1 | R2 | R3 | R4 | R5 | R8 | C1 | C2 | Fuzziness  |

| N              | F <sub>1</sub>   | 45              | 7  | 4  |    |    |    |    |    | 2  | 6 (R1,R2)  |

|                | $F_2$            | 64              |    |    |    |    |    |    |    |    |            |

| R1↑            | F <sub>1</sub>   | 6               | 47 | 9  |    |    |    |    |    |    | 2 (R1,R2)  |

|                | $F_2$            |                 | 62 | 2  |    |    |    |    |    |    |            |

| R2↑            | F <sub>1</sub>   |                 | 8  | 51 | 1  |    |    |    |    |    | 4 (R1,R2)  |

|                | $F_2$            |                 | 2  | 61 |    |    |    |    |    |    | 1 (R1,R2)  |

| R3↓            | F <sub>1</sub>   |                 |    | 3  | 42 | 7  |    |    | 2  |    | 10 (R3,R4) |

|                | $F_2$            |                 |    |    | 59 | 2  |    |    |    |    | 3 (R3,R4)  |

| R4↑            | F <sub>1</sub>   |                 |    |    | 9  | 44 |    |    | 3  |    | 8 (R3,R5)  |

|                | $F_2$            |                 |    |    | 1  | 61 |    |    |    |    | 2 (R3,R4)  |

| R5↓            | F <sub>1</sub>   |                 |    |    |    |    | 48 | 9  | 2  | 1  | 4 (R5,R8)  |

|                | $F_2$            |                 |    |    |    |    | 62 | 2  |    |    |            |

| R8↓            | F <sub>1</sub>   |                 |    |    |    |    | 11 | 46 |    | 4  | 3 (R8,C2)  |

|                | F <sub>2</sub>   |                 |    |    |    |    | 3  | 61 |    |    |            |

| C1↓            | F <sub>1</sub>   |                 |    |    | 3  | 7  | 4  |    | 41 |    | 9 (C1,R4)  |

|                | F <sub>2</sub>   |                 |    |    |    | 3  |    |    | 58 |    | 3 (C1,R4)  |

| C2↑            | F <sub>1</sub>   |                 |    |    |    |    | 3  | 6  |    | 49 | 6 (C2,R8)  |

**Table 1.** Segment of test results based on single frequency F<sub>1</sub> and information fusion method F<sub>2</sub>.

(ii) 64 kinds of soft faults resulted from parameter variation considering  $|\Delta X_j|/X_j$  (j = 1, 2, ..., 8) as 0.02, 0.1, 10 and 50.

Then the total value of the circuit modes *M* defined in (10) equals 81 including the normal one. It is convenient to change waveform kinds or increase the number of testing samples by using the frequency sweep method with DDS technology. So we generated 210 excitation signals to calculate the feather interval vectors, then 64 of which are chosen as the test samples to identify the efficiency and accuracy of diagnosis algorithm, According to the training method based on neural network proposed in [28], the decision thresholds chosen in this algorithm are  $\delta = 0.82$ ,  $\sigma = 0.18$ ,  $\lambda = 1.75$ .

Results presented in Table 1 illustrate the comparison details between the single frequency method at  $1258.93 \,\mathrm{Hz}$  (derived from  $10^{0.05*62}$ ) and the fusion method based on 146 frequency responses defined in (15), and we define the two methods as  $F_1$  and  $F_2$  in Table 1. It can be clearly seen that method  $F_1$  has a lower rate of accuracy and more fuzziness, while applying method F<sub>2</sub> these figures are improved dramatically. The reason is that the feature interval vectors of different frequency responses have complementary information especially to this kind of non-linear or approximately linear network, which can be fused to a more reliable location conclusion.

Table 2 indicates that the proposed information fusion approach can increase the diagnosis accuracy reliably, the final average accuracy rate is high up to approximately 96%. At the same time, because of the parallel data processing ability provided by FPGA, the total time consumption is no more than some 60 ms. In addition, as a result of the wide bandwidth (0-20 MHz) and real-time fault decision mechanism, the proposed scheme and implemented system possess strong vitality and adaptability for fault diagnosis and location of analog circuit.

**Table 2.** Fault diagnosis performance evaluation.

| Category<br>(based on) | Rate of correctness (%) | Rate of<br>mistake (%) | Rate of refusal (%) | Time consumption (ms) |

|------------------------|-------------------------|------------------------|---------------------|-----------------------|

| Node voltage           | 75.46                   | 23.19                  | 1.35                | 18.7                  |

| A–F                    | 71.28                   | 19.08                  | 9.64                | 34.5                  |

| P–F                    | 69.52                   | 20.29                  | 10.19               | 36.3                  |

| Fusion                 | 97.54                   | 2.15                   | 0.31                | 57.6                  |

# 6. Conclusion

A real-time and cost-effective fault detection and diagnostic methodology for analog circuits has been realized on the customized FPGA platform, and its abundant acquisition channels gather the accessible node voltages, information of amplitude-frequency and phase frequency of analog circuits. It can identify the hard and soft faults reliably with around 96% detection rate, benefiting from the information fusion, orthogonal techniques and interval math theory based on multiple circuit features. When compared with the traditional PC-based approach, our diagnosis method is more efficient as a result of the speedy and parallel data processing ability provided by FPGA. The offered Ethernet interface facilitates the remote monitoring and controlling in production which is superior to the RS232 interface in [29] to some extent. However, because the neural networkbased training method is computationally complex, we have to spend a certain time expense on the calculation of the decision thresholds  $\delta$ ,  $\sigma$  and  $\lambda$ . Our another PCI express blade system equipped with larger resource FPGA is currently being developed, which is expected to be able to reduce the training time consumption. And improving the algorithm on hardware programming plays the significant part in real-time diagnosis, which also needs further research.

# 310 (4

### **Disclosure statement**

No potential conflict of interest was reported by the authors.

# **Funding**

This work was financially supported by the National Natural Science Foundation of China [Grant number: 51704089], the Anhui Provincial Natural Science Foundation of China [Grant number: 1808085QF190], the China Postdoctoral Science Foundation [Grant number: 2017M621996], the Fundamental Research Funds for the Central Universities of China [Grant number: JZ2018YYPY0296] and the PhD Special Research Fund of HFUT [Grant number: JZ2016HGBZ1030].

# **ORCID**

Qiwu Luo http://orcid.org/0000-0003-2822-5538

## References

- [1] Tulloss RE. Fault dictionary compression: recognizing when a fault may be unambiguously represented by a single failure detection. Proc. of Test Conf., Nov. 1980, pp. 368–370.

- [2] Zou W, Cheng WT, Reddy SM, et al. Speeding up effectcause defect diagnosis using a small dictionary. IEEE VLSI Test Symp., Berkeley, CA, USA, May 6–10, 2007, pp. 225–230.

- [3] Hochwald W, Bastian JD. A dc approach for analog fault dictionary determination. IEEE Trans. Circuits Syst. 1979;26(7):523–529.

- [4] Salama AE, Amer FZ. Parameter identification approach to fault diagnosis of switched capacitor circuits. IEE Proc. G Circuits Devices Syst. 1992;139(4): 467–472.

- [5] Tadic P, Đurović Ž, Kovačević B, et al. Fault diagnosis for steam separators based on parameter identification and CUSUM classification. IEEE Int. Conf. of Ind. Technol. (ICIT), Athens, Greece, Mar. 19–21, 2012, pp. 248–253.

- [6] Robotycki A, Zielonko R. Some models and methods for fault diagnosis of analog piecewise linear circuits via verification technique. Proc. of the 17th IEEE Instrum. and Meas. Technol. Conf., Baltimore, USA, May 01–04, 2000, vol. 2, pp. 1050–1055.

- [7] He Y, Tan Y, Sun Y. A neural network approach for fault diagnosis of large-scale analog circuits. IEEE Int. Symp. Circuits Systems (ISCAS). May 26–29, 2002;1: I-153–I-156.

- [8] Mourad E, Nayak A. Comparison-based system-level fault diagnosis: a neural network approach. IEEE Trans Parallel Distrib Syst 2012;23(6):1047–1059.

- [9] Wang P, Yang S. A new diagnosis approach for handling tolerance in analog and mixed-signal circuits by using fuzzy math. IEEE Trans. Circuits Syst. I Reg. Papers. 2005;52(10):2118–2127.

- [10] Stopjakova V, Malosek P, Matej M, et al. Defect detection in analog and mixed circuits by neural networks using wavelet analysis. IEEE Trans. Rel. 2005;54(3):441–448.

- [11] Bandler JW, Salama AE. Fault diagnosis of analog circuits. Proc IEEE. 1985;73(8):1279–1325.

- [12] Prieto JA, Rueda A, Grout I, et al. An approach to realistic fault prediction and layout design for testability in analog circuits. Proceedings Design, Automation and

- Test in Europe; Feb 23–26; Paris, France. IEEE; 1998. p. 905–911.

- [13] Variyam PN, Cherubal S, Chatterjee A. Prediction of analog performance parameters using fast transient testing. IEEE Trans. Comput. Aided Design Integr. Circuits Syst. 2002;21(3):349–361.

- [14] Peng M, He Y, He J. A new method for fault detection and location of analog circuits. J. Electron Meas. Instrum. 2006;20(1):10–14.

- [15] Yang Q, Zhu Y, Wu F. Remote intelligent fault diagnosis of analog circuit. IEEE Int. Conf. on Natural Comput. (ICNC), Shanghai, China, July 26–28, 2011, vol. 3, pp. 1677–1680.

- [16] Karimi S, Gaillard A, Poure P, et al. FPGA-based real-time power converter failure diagnosis for wind energy conversion systems. IEEE Trans. Ind. Electron. 2008;55(12):4299–4308.

- [17] Medina LMC, de Jesus Romero-Troncoso R, Cabal-Yepez E, et al. FPGA-based multiple-channel vibration analyzer for industrial applications in induction motor failure detection. IEEE Trans Instrum Meas 2010;59(1):63–72.

- [18] Buerkle T, LaMeres BJ, Kaiser T, et al. Ionizing radiation detector for environmental awareness in FPGA-based flight computers. IEEE Sensors J. 2012;12(6):2229–2236.

- [19] Jurišić D, Mijat N, Cosic V. Frequency domain approach to fault diagnosis of analog filters. IEEE Int. Conf. Electron., Circuits Syst. (ICECS 1996), Rodos, Greece, Oct. 13–16, 1996, vol. 2, pp. 1135–1138.

- [20] Jurišić D, Mijat N, Stojkovic N. Dictionary optimization in fault analysis applying binary logical manipulation algorithm. Proc. IASTED Int. Conf. Signal Image Process, Las Vegas, USA, Oct. 28–31, 1998, pp. 661–664.

- [21] Peng M, Yigang XH. Soft-fault detection and location for circuits with tolerance. Trans. China Electrotechnical Society. 2009;24(3):222–228.

- [22] Ye L, Wang H. Node voltage increment ratio fault dictionary and its' geometric models for linear analog soft fault diagnosis with tolerance. IEEE Circuits and Systems Int. Conf. on Testing and Diagnosis (ICTD 2009), Chengdu, China, Apr. 28–29, 2009, pp. 1–4.

- [23] Nilsson P, Torkelson M. A custom digital intermediate frequency filter for the American mobile telephone system. IEEE J Solid-State Circuits. 1997;32(6):806–815.

- [24] Peng M, He Y, Lv J. Fault location of analog circuits using intelligent information fusion technology. Trans. China Electrotech Soc. 2005;20(11):93–96.

- [25] Bormann D, Frischen AR, Schrey M, et al. A notch filter alignment circuit for wireless communication FDD systems. Asia-Pacific Microw. Conf. Proc., Yokohama, Japan, Dec. 7–10, 2010, pp. 1308–1311.

- [26] Sarkar P, Ghatak R, Pal M, et al. Compact UWB bandpass filter with dual notch bands using open circuited stubs. IEEE Microw. Wireless Compon. Lett. 2012;22(9):453–455.

- [27] Abderrahman A, Cerny E, Kaminska B. Worst case tolerance analysis and CLP-based multifrequency test generation for analog circuits. IEEE Trans. Comput. Aided Design Integr. Circuits Syst. 1999;18(3):332–345.

- [28] Minfang P, Meie S, Yigang H, et al. Analog circuit diagnosis using RBF network and D-S evidential reasoning. Trans. China Electrotech Soc. 2009;24:6–13.

- [29] Wangxing Y, Yigang H, Wenji Z, et al. Application of BP neural network in vessel circuits fault diagnosis tester. Comput Meas Control. 2009;17(8):1565–1567.